# PARTITIONING-DRIVEN CONVERGENCE IN THE DESIGN OF RANDOM-LOGIC BLOCKS

#### A DISSERTATION

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING

AND THE COMMITTEE ON GRADUATE STUDIES

OF STANFORD UNIVERSITY

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

Hema Kapadia May 2000

©Copyright by Hema Kapadia 2000 All Rights Reserved I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

> Mark Horowitz (Principal Adviser)

I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

Giovanni De Micheli

I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

Balaji Prabhakar

Approved for the University Committee on Graduate Studies:

### Abstract

The conventional methodology for computer-aided design of random-logic blocks requires several iterations of logic synthesis and layout tools, and a significant amount of manual intervention, before converging to an implementation that meets the design's constraints. This thesis proposes *Nebula*, a new design flow that uses netlist partitioning to achieve an optimal trade-off between two conflicting requirements for design convergence: accurate wire-load modeling in synthesis and merging incremental netlist optimizations into layout. The flow iterates between low-level synthesis, layout and re-partitioning optimizations. An experimental prototype, which emulates the *Nebula* flow, was developed to explore its viability and limitations.

A partitioning scheme, implemented in the prototype system, accurately models global wires during synthesis, while allowing room for incremental optimizations in local logic. Experimental results show that in spite of overheads of optimizing a partitioned netlist, accurate wire-load modeling narrows the gap between post-synthesis and post-layout timing in the prototype system. This leads to a faster design convergence as opposed to the conventional methodology.

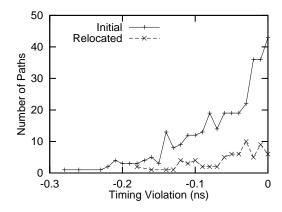

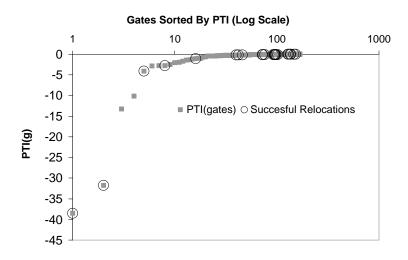

A timing-driven repartitioning heuristic was implemented, which improves post-layout timing by reducing the contribution of global wire-loads along critical paths. Results show that relocating 1% of all gates in a design prunes out 80% of its critical paths. However, the scope of worst-case timing improvements is limited by the ability to merge relocations into the existing layout.

### Acknowledgments

My journey to this dissertation was made possible by the guidance, encouragement and support of several people. I would like to take this opportunity to thank them.

I am grateful to my advisor, Prof. Mark Horowitz, who gave me the dream opportunity to join Stanford University as his research assistant. Working with him for the last seven years has been an enriching experience. I hope to have imbibed a small part of his ability to see right through the crux of a problem, and the "let's take a step back" attitude. I would like to thank him for his guidance and patience, for providing generous resources, and for setting high standards.

My associate advisor, Prof. Giovanni De Micheli, enabled my transition into the field of CAD research. I am thankful to him for his guidance and encouragement, for introductions to industry personnel in this field, and for providing unlimited access to his office library. Thanks to Prof. Kunle Olukotun for participating in my oral defense committee. I would like to thank Prof. Balaji Prabhakar who chaired my orals committee, and generously read this thesis for approval while accommodating my deadlines in his busy schedule.

Thanks to Russ Segal and Dwight Hill at Synopsys for helpful discussions, and for providing access to the *Design Compiler* code. Thanks to Prof. Eby Friedman from University of Rochester for introducing me to the joy of reading technical papers, and to Prof. Alexander Albicki for introducing me to the joy of writing technical papers.

I am indebted to members of the Stanford FLASH multiprocessor team for rookie guidance, and for making me a "tough cookie" over the four years on the project. I learnt a lot from their combined technical genius. Specifically, I would like to thank Prof. John Hennessey and Prof. Mendel Rosenblum for their mentorship. Special

thanks to Ricardo Gonzalez, Mark Heinrich, Dave Ofelt, Dave Nakahira and Rich Simoni for their friendship and guidance.

This thesis was made much more readable after Deborah Harber's proof-reading comments. I would like to thank her for the timely help and encouragement. Thanks to Kathleen DiTommaso and Darlene Hadding for crucial administrative support.

I am fortunate to have had very smart and very friendly colleagues. I would like to thank my office-mate Jeff Solomon for the frequent exchange of strong opinions and for his help with LSI tools, .cshrc files, and all things UNIX. Special thanks to Evelina Yeung for her friendship, moral support and motivating talks about life after graduation. Jules Bergmann developed, and yes, supported the *Vex* system, which was crucial for this work. Ron Ho and Ken Mai thoroughly reviewed everything I ever published. Thanks also to Shankar Govindaraju, Luca Benini, and other fellow graduate students who made it a stimulating research environment.

I am thankful to Anju Gupta, Rajiv Kapur, Yashika Deva, Paddy-Gargi Mamtora and all other local friends who helped me keep a balanced outlook, consoled me through stressful times, and persistently asked me the "are you done yet?" question. Special thanks to Raja for never letting me procrastinate. I am thankful to Girish Dahake, Vivek Vohra, Sujeet Kumar, Raka Chakravarty, Victor Adler, Falguni Shah and Kokilaben Tirvedi for the positive influence of their friendships at crucial junctures in my life.

I owe everything I am to the upbringing my family gave me, and to their strong belief in my abilities. Thanks to my parents for letting me go far from home for better education. I am grateful for the unconditional love and nurturing of my sister Hansa who taught me how to read and write, and of my sister-in-law Pushpa. Thanks to my two brothers Hridaynath and Ashutosh, brother-in-law Harshadbhai and sister-in-law Ketkibhabhi, who always ensured of my growth and happiness. I would also like to thank my in-laws for their support.

And last but not least, I would like to thank and congratulate my husband Atul for surviving the last five years of my student life. I could not have done this without his love, encouragement, and creative perspective on technical as well as life matters.

# Contents

| Abstract       |                 |                           |                                             |    |  |

|----------------|-----------------|---------------------------|---------------------------------------------|----|--|

| $\mathbf{A}$   | Acknowledgments |                           |                                             |    |  |

| 1 Introduction |                 |                           | ion                                         | 1  |  |

| 2              | Bac             | kgrou                     | nd                                          | 7  |  |

|                | 2.1             | Design                    | n of the MAGIC Chip                         | 7  |  |

|                |                 | 2.1.1                     | Chip-level Planning                         | 10 |  |

|                |                 | 2.1.2                     | Gate-level Implementation                   | 12 |  |

|                | 2.2             | Conve                     | ntional Design Flow                         | 13 |  |

|                |                 | 2.2.1                     | Static Timing Analysis                      | 14 |  |

|                |                 | 2.2.2                     | Wire-load Estimation                        | 15 |  |

|                |                 | 2.2.3                     | Full Synthesis                              | 17 |  |

|                |                 | 2.2.4                     | Initial Cell-Placement                      | 18 |  |

|                |                 | 2.2.5                     | Detailed Cell-Placement                     | 19 |  |

|                |                 | 2.2.6                     | Reoptimization and Layout-Merge             | 20 |  |

| 3              | Bri             | dging 1                   | the Gap Between Synthesis & Layout          | 23 |  |

|                | 3.1             | Synth                     | esis-driven Layout                          | 24 |  |

|                | 3.2             | 2 Layout-driven Synthesis |                                             |    |  |

|                |                 | 3.2.1                     | Timing Analysis for Layout-driven Synthesis | 27 |  |

|                |                 | 3.2.2                     | Buffering and Sizing                        | 28 |  |

|                |                 | 3.2.3                     | Relocation and Re-wiring                    | 29 |  |

|   |            | 3.2.4   | Logic Restructuring                                           | 30 |

|---|------------|---------|---------------------------------------------------------------|----|

|   | 3.3        | Simul   | taneous Synthesis and Layout                                  | 31 |

|   |            | 3.3.1   | Simultaneous Technology Mapping and Linear Placement          | 31 |

|   |            | 3.3.2   | Iterating Constraint Generation, Synthesis, and Floorplanning | 32 |

| 4 | <b>A</b> ( | CAD F   | low Targeting Design Convergence                              | 35 |

|   | 4.1        | An Inc  | dustry Tool for Design Convergence                            | 36 |

|   | 4.2        | Archit  | secture of $Nebula$                                           | 37 |

|   |            | 4.2.1   | Partitioning and Wire-load Estimation                         | 40 |

|   |            | 4.2.2   | Cluster Placement                                             | 42 |

|   |            | 4.2.3   | Synthesizing Partitioned Logic                                | 42 |

|   |            | 4.2.4   | Detailed Cell-placement in a Partitioned Layout               | 43 |

|   |            | 4.2.5   | Timing-driven Repartitioning                                  | 44 |

|   | 4.3        | An Ex   | xperimental Prototype                                         | 45 |

|   |            | 4.3.1   | Initial Synthesis and Partitioning                            | 46 |

|   |            | 4.3.2   | Floorplanning                                                 | 46 |

|   |            | 4.3.3   | Resynthesis with a Hybrid Wire-load Model                     | 47 |

|   |            | 4.3.4   | Detailed Cell-placement                                       | 48 |

|   |            | 4.3.5   | Timing-driven Repartitioning                                  | 48 |

|   | 4.4        | Summ    | ary                                                           | 49 |

| 5 | Par        | titioni | ng for Better Wire-Load Models                                | 51 |

|   | 5.1        | A Hyb   | orid Wire-load Model for Logic Synthesis                      | 52 |

|   |            | 5.1.1   | Back-annotation from Layout                                   | 52 |

|   |            | 5.1.2   | Wire-load Models for Local Nets                               | 54 |

|   |            | 5.1.3   | Wire-load Models for Global Nets                              | 54 |

|   | 5.2        | Partit  | ioning Scheme                                                 | 55 |

|   |            | 5.2.1   | Identifying Cluster Boundaries                                | 56 |

|   |            | 5.2.2   | Merging Small Clusters                                        | 57 |

|   |            | 5.2.3   | Maximum Cluster Size                                          | 60 |

|   | 5.3        | Exper   | imental Results                                               | 64 |

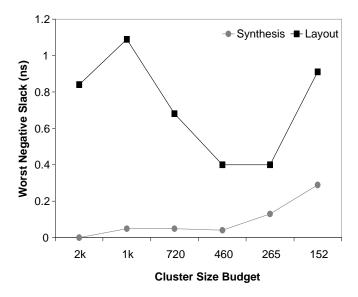

|   |            | 5.3.1   | Maximum Cluster Size for the Prototype System                 | 65 |

|    |                    | 5.3.2                        | Comparison of the Gap Between Synthesis and Layout        | 68  |

|----|--------------------|------------------------------|-----------------------------------------------------------|-----|

|    | 5.4                | Summ                         | ary                                                       | 74  |

| 6  | Tim                | Timing-driven Repartitioning |                                                           |     |

|    | 6.1                | Heuris                       | tic for Gate Relocation                                   | 76  |

|    |                    | 6.1.1                        | Motivation for Path Enumeration                           | 78  |

|    |                    | 6.1.2                        | Potential For Timing Improvement                          | 80  |

|    | 6.2 Implementation |                              | nentation                                                 | 82  |

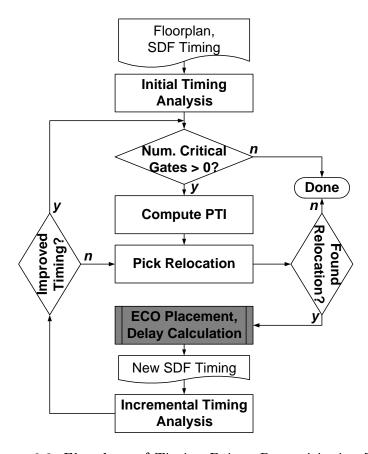

|    |                    | 6.2.1                        | Initial Timing Analysis                                   | 83  |

|    |                    | 6.2.2                        | Computing $PTI$                                           | 85  |

|    |                    | 6.2.3                        | Picking a Relocation                                      | 85  |

|    |                    | 6.2.4                        | ECO Placement                                             | 86  |

|    |                    | 6.2.5                        | Incremental Timing Analysis                               | 86  |

|    |                    | 6.2.6                        | Measuring Timing Improvement                              | 87  |

|    | 6.3                | Experi                       | mental Results                                            | 87  |

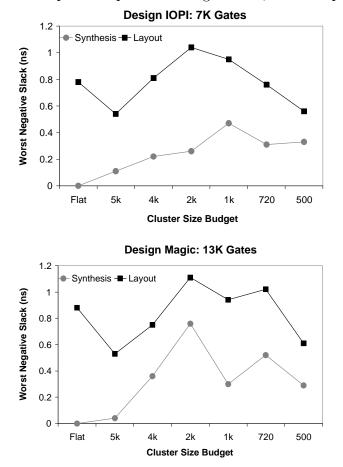

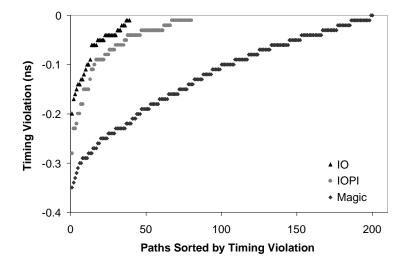

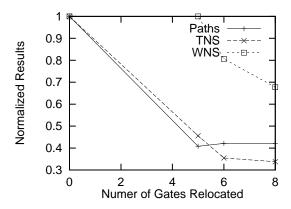

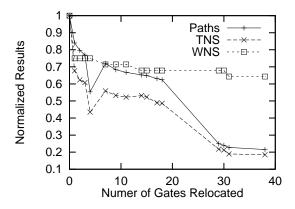

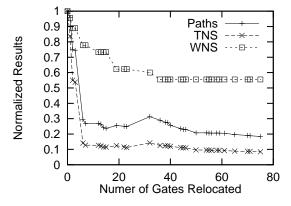

|    |                    | 6.3.1                        | Incremental Timing Improvements                           | 87  |

|    |                    | 6.3.2                        | Design Speed                                              | 89  |

|    |                    | 6.3.3                        | Overall Timing Quality                                    | 90  |

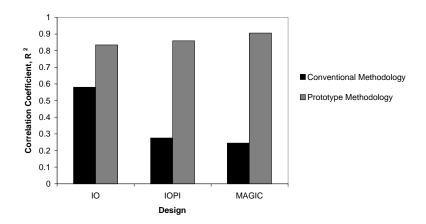

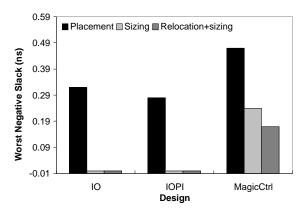

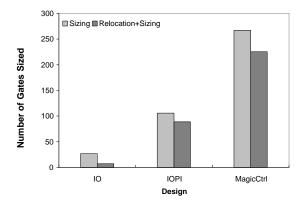

|    |                    | 6.3.4                        | Applying Relocation with Driver-Sizing                    | 91  |

|    | 6.4                | Future                       | Work                                                      | 93  |

|    |                    | 6.4.1                        | Extending the Scope of Relocations with Logic Duplication | 93  |

|    |                    | 6.4.2                        | Extending the Scope of Layout Merges                      | 94  |

|    | 6.5                | Summ                         | ary                                                       | 96  |

| 7  | Con                | Conclusions                  |                                                           |     |

|    | 7.1                | Future                       | Work                                                      | 98  |

|    |                    | 7.1.1                        | Synergy of Post-Layout Optimization Techniques            | 99  |

|    |                    | 7.1.2                        | Soft Boundaries in Synthesis and Layout Optimizations     | 99  |

| Bi | ibliog             | graphy                       |                                                           | 101 |

# List of Tables

| 5.1 | Benchmark Designs                                     | 64 |

|-----|-------------------------------------------------------|----|

| 5.2 | Number of Partitions Created in the Benchmark Designs | 68 |

| 6.1 | Paths Leading to the Worst-Case Endpoint              | 78 |

| 6.2 | Timing Results After Relocation                       | 89 |

| 6.3 | Timing Quality After Relocation                       | 90 |

# List of Figures

| 2.1  | Block Diagram of MAGIC                                       | 8  |

|------|--------------------------------------------------------------|----|

| 2.2  | Floorplan of MAGIC                                           | 11 |

| 2.3  | Conventional Methodology                                     | 14 |

| 2.4  | Limitation of Statistical Wire-Load Models                   | 16 |

| 2.5  | Conventional Methodology with Post-Layout Optimizations      | 21 |

| 3.1  | Example of Duplications Required in Wireplanning             | 25 |

| 4.1  | Nebula - A CAD Flow Targeting Design Convergence             | 38 |

| 4.2  | Example of Technology Mapping Across Clusters                | 43 |

| 4.3  | Prototype Design System                                      | 45 |

| 5.1  | Example Floorplan for Hybrid Wire-Load Modeling              | 53 |

| 5.2  | Example Netlist for MFFC Clustering                          | 56 |

| 5.3  | Pseudo code of Partitioning Procedure                        | 58 |

| 5.4  | A Case For Collapsing Single-Fanout Nets                     | 59 |

| 5.5  | A Case For Blind Merge Of Clusters                           | 60 |

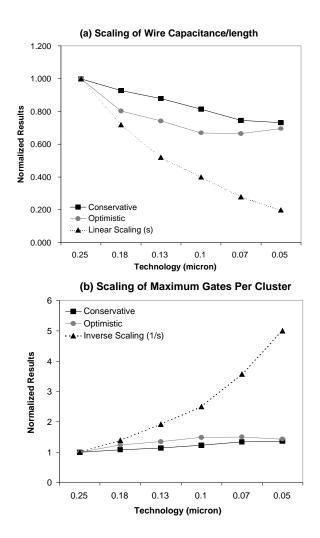

| 5.6  | Scaling Predictions for $C_{wire/\mu m}$ , and Max_Num_Gates | 63 |

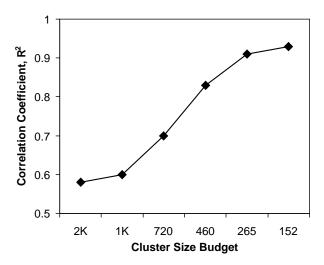

| 5.7  | Wire-load Correlation Vs. Maximum Cluster-Size               | 66 |

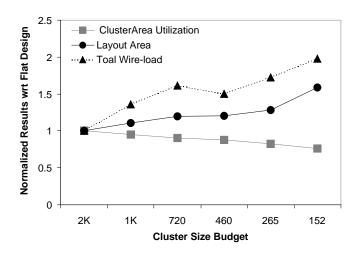

| 5.8  | Layout Overheads Vs. Maximum Cluster-Size                    | 67 |

| 5.9  | Timing Violations Vs. Maximum Cluster-Size                   | 68 |

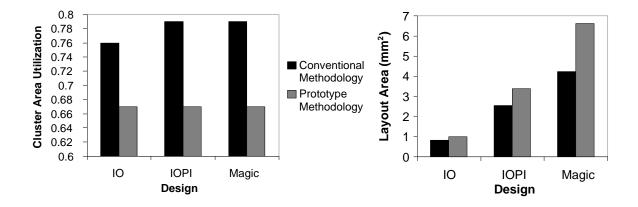

| 5.10 | Layout Overhead in the Prototype System                      | 69 |

| 5.11 | Synthesis Overhead in the Prototype System                   | 70 |

| 5.12 | Comparison of Wire-load Correlation                          | 71 |

| 5.13 | Accuracy of Wire-load Models in the Prototype System         | 72 |

|------|--------------------------------------------------------------|----|

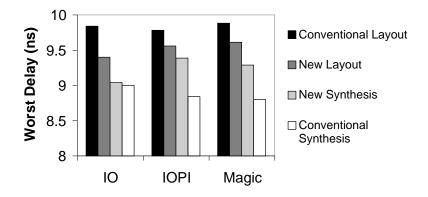

| 5.14 | Comparison of Worst-case Delays                              | 73 |

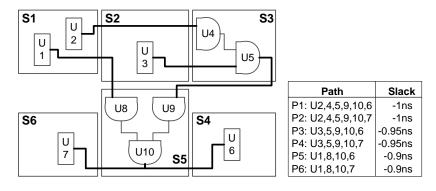

| 6.1  | Paths Leading to the Worst-Case Endpoint                     | 78 |

| 6.2  | Example Netlist for Timing-driven Repartitioning             | 79 |

| 6.3  | Flowchart of Timing-Driven Repartitioning Tool               | 83 |

| 6.4  | Timing Improvements Through Successive Relocations : $IO$    | 88 |

| 6.5  | Timing Improvements Through Successive Relocations : $IOPI$  | 88 |

| 6.6  | Timing Improvements Through Successive Relocations : $Magic$ | 88 |

| 6.7  | Timing Quality: IOPI                                         | 91 |

| 6.8  | Comparison of Worst Negative Slack                           | 92 |

| 6.9  | Comparison of Number of Gates Sized                          | 92 |

| 6.10 | PTI of gates and Successful Relocations                      | 95 |

# Chapter 1

### Introduction

Chip design is a complex problem that needs constant innovation to keep up with increasing size, functional complexity and performance of single-chip systems. Computeraided design tools are used to optimize the logical implementation of a chip as well as to determine the physical locations and interconnections of various components on the chip. Picking the correct logical structure depends on the physical topology, but the physical topology changes with changing logical structures. In early computeraided design (CAD) tools this coupling between logical and physical design was not handled directly. Instead the designer went through several iterations of logical and physical design, refining the view of one with respect to the latest implementation of the other. These refinements made non-incremental changes to the design description, resulting in a flow that sometimes failed to converge to an implementation that met the design's constraints. To aid convergence, the designer had to manually intervene by making small changes to the logical or physical implementation, or by changing the specification of the design in order to help the chip through the tool flow. As design complexity has increased, this lack of convergence in the conventional design tools has become problematic and new tools that bridge logical and physical design are starting to appear. This thesis explores some of the issues that need to be addressed to fully integrate logical and physical design.

This work in CAD methodology grew out of our experience with a large chip-design project at Stanford University. Our team of six students designed a 2M transistor

ASIC called MAGIC in a  $0.5\mu m$  standard-cell technology. Chapter 2 presents both an overview of the computer-aided design flow used on MAGIC and the tools involved at various stages of the chip-design process. Trouble at the lowest level of the conventional CAD tool flow, which consists of time-consuming iterations between logic synthesis and layout of each random-logic block before arriving at its final gate-level implementation, motivated this work. Initial logic synthesis steps in this flow use approximate wire-load predictions before the layout is determined. Inaccuracies in these predictions result in new timing paths after layout that were not foreseen by synthesis. Later synthesis steps optimize the logic along these timing paths by making small local changes to the netlist using accurate wire-load information from the existing layout. However, layout tools have a limited ability to incorporate such netlist changes without perturbing the locations of the unchanged logic. Such perturbations end up nullifying the wire-load assumptions made by local synthesis refinements, resulting in another set of unforeseen timing paths. There is no guarantee that an iteration of synthesis, followed by layout, will lead to incremental improvements in the netlist. Hence, there is no upper bound on the number of iteration required in order to arrive at an implementation that meets the design's performance target. This problem is widely referred to as a lack of design convergence (or closure), or more specifically as a lack of timing convergence (or closure). While ideally the design flow should have no iterations, the industry average today is 8 iterations for a typical design to reach timing closure [1]. Over-design is an expensive workaround often used, where the performance target of the design is significantly lower than what can be achieved with its underlying technology.

This lack of convergence in the conventional CAD flow is expensive due to the amount of design effort and resources required to meet a design's performance and time-to-market targets. Hence, bridging the gap between synthesis and layout tools has been an active area of research in recent years. Several techniques have been proposed for improving convergence in the conventional flow through incremental netlist refinements [2], [3], [4], [74], [6] [7]. Also, new design flows have been proposed that change the nature of interaction between synthesis and layout to make iterations between the two more incremental and productive [8], [9], [10]. Another methodology

is being explored to turn the optimization flow around in such a way that it does not require iterations [11], [12]. Chapter 3 provides an overview of these techniques.

The discussion about related research will lead to the architecture of Nebula, our proposal for a CAD flow that targets design convergence by merging logic synthesis and layout in a unified tool. This flow is presented in Chapter 4. Low-level synthesis and layout transforms are iterated in Nebula, to keep a consistent view of wire-loads and timing throughout the optimization flow. Timing is checked after each low-level synthesis change is picked and merged into the current layout, before incorporating the change into the netlist. Nebula employs netlist partitioning to reach a middle ground between two conflicting requirements: accurate wire-load modeling and incremental optimizations. Netlist partitioning creates regions of placement consisting of small logic clusters. Low-level synthesis decisions are iterated with cluster placement while maintaining soft cluster boundaries that have irregular shapes and allow movement of logic across them. Wire-loads are estimated accurately and updated consistently by using the exact placement of the clusters and the approximate regions of placement of individual gates within clusters. If incremental changes made by synthesis change the sizes of clusters, cluster placement is updated along with the wire-load of inter-cluster nets. Incremental changes made to local logic within each cluster are absorbed by the layout without affecting any wire-loads, because local wire-loads are modeled based on the area of the clusters and not on the exact placement of individual gates.

Several challenging problems need to be solved before a CAD system can be built based on Nebula. While netlist partitioning creates accurate wire-load models in this flow, it also reduces the optimization space of synthesis and layout algorithms. A key challenge is to find a partitioning scheme that achieves the best trade-off between predictability and optimization space. Partitioning a netlist early in the design flow pushes the prediction problem from synthesis into partitioning, where wrong logic may cluster together due to lack of accurate physical information. A post-layout repartitioning scheme needs to be added to this flow to improve timing by relocating logic across partition boundaries. A prototype design methodology that emulates the Nebula design flow was created using conventional synthesis and layout tools, to serves as an experimentation platform that allows us to study the viability and limitations of

Nebula for improving design convergence. Implementation of the prototype system is presented in the second half of Chapter 4. Chapters 5 and 6 use the prototype system to experiment with our solutions to some of the challenges of the Nebula design flow.

Chapter 5 explores a hybrid wire-load model that uses a combination of cluster placement and areas of individual cell-placement to derive accurate estimates for global (inter-cluster) wire-loads and approximate estimates for local (intra-cluster) wire-loads. Wires that are likely to be modeled inaccurately by approximate wireload models are identified from the netlist structure, and the netlist is then partitioned along those wires. Since synthesis transforms can now use accurate estimates of global wires, such partitioning maximizes the impact of this wire-load model by applying it to the "problematic wires" in the netlist. Next, the maximum cluster size is derived, with the objective to allow incremental layout while keeping approximately modeled local wires predictable. This objective minimizes the impact of potential inaccuracies in wire-load predictions on netlist timing. Comparing these partitioning and wire-load modeling solutions with the conventional methodology, experimental results show that making wire-loads predictable and widening the scope of incremental layout through netlist partitioning enables faster convergence to the desired final design implementation. However, the experiments also show that the lack of soft cluster boundaries in the prototype system results in area and timing overheads due to reduced optimization spaces of synthesis and layout tools.

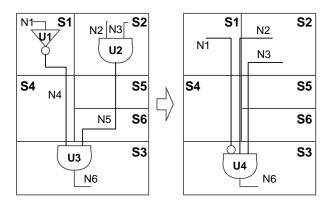

As a first step towards creating soft partition boundaries, Chapter 6 presents a heuristic for moving logic across partitions based on post-layout timing analysis. The heuristic identifies gates that add significant global wire-length to many timing-critical paths due to the physical locations of their parent clusters, and relocates them to another cluster that appears just before or just after those gates along many critical paths. Experimental results show that while the heuristic gives marginal improvement in the worst-case delay, it significantly reduces the total number of critical paths in a design. This heuristic is also applicable within the context of the conventional methodology as another post-layout optimization technique for helping designs meet timing targets at a late stage in the CAD methodology, without having to resort to manual intervention or iterations with synthesis.

Finally, Chapter 7 concludes this thesis. The key observation is that accurate wire-load modeling and incremental layout capability in the *Nebula* design flow reduces the gap between synthesis and layout views of wire-loads and timing. Adding a timing-driven repartitioning step further helps convergence in this flow by correcting early partitioning decisions based on the latest timing. However, the scope of all post-layout optimization techniques is limited by their ability to merge changes into the existing layout. Future research needs to explore using several different techniques together to get the most benefit from them. An important area of future research towards design convergence is creation of synthesis and layout tools that optimize a partitioned netlist without incurring any overheads, by the treating partition boundaries as soft boundaries.

### Chapter 2

# Background

Our work in CAD methodology grew out of a computer architecture research program at Stanford called FLASH, which explored building a large-scale distributed-shared-memory multiprocessor. The core of the FLASH machine was MAGIC, a 2M transistor ASIC which acted as the memory controller for each node in the multiprocessor [13]. The design of this chip used a conventional CAD flow which consisted of initial floorplanning, global routing and timing estimation at the chip level, followed by logic synthesis, detailed placement and routing within each random-logic block at the gate level. This chapter first presents the conventional chip-level CAD flow in the context of large designs such as MAGIC, and next focuses on the methodology for gate-level implementation of individual blocks. The optimization flow of the gate-level CAD methodology is described, including a summary of individual CAD tools that make up its building blocks. This discussion will show a lack of convergence in this flow stemming from loose coupling between logic synthesis and layout, and also from non-incremental optimizations that result in an inconsistent view of wire-loads among the various steps of the flow.

### 2.1 Design of the MAGIC Chip

Design of the MAGIC chip started with the system architecture of FLASH, a FLexible Architecture for SHared memory. FLASH is intended to provide a common hardware platform on which the relative merits of different memory sharing protocols are studied [14, 15, 16]. Each node of the FLASH machine contains: a high-performance off-the-shelf microprocessor used as the compute processor, a portion of the machine's global memory, a network port connecting the node to the rest of the machine, I/O devices, and a custom node controller chip - MAGIC, MAGIC, Memory And General Interconnect Controller, handles all communication within the node as well as between the node and the network. It moves data between the components of the node, and manipulates the state of the corresponding memory locations to comply with the memory sharing protocol being executed.

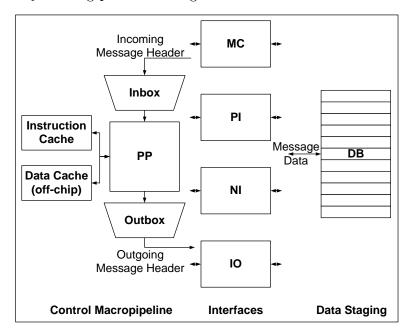

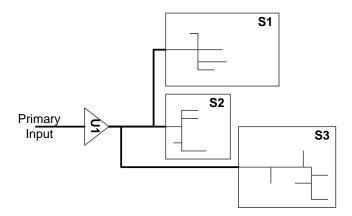

Figure 2.1: Block Diagram of MAGIC

The architectural definition of MAGIC was driven by three factors: its functional definition, the requirement for flexibility of running different memory sharing protocols, and the goal of operating at low latency and high bandwidth to ensure that the flexibility does not come at the cost of performance overhead. Figure 2.1 shows the MAGIC architecture in a block diagram. The functional definition of MAGIC called for three blocks that interface to external components of the node: a processor interface (PI) to the compute processor, I/O interface (IO) to the PCI bus [17], and a network port interface (NI). We added a memory controller (MC) block to

Data communication between the interface blocks and manipulation of memory state are controlled by the protocol processor block (PP), which is a programmable RISC core giving flexibility to run any memory-sharing protocol. While the protocol code and data reside in a reserved portion of the node's main memory, we added data and instruction caches to enable high-speed access to protocol code and data used frequently by the PP. Furthermore, we separated data movement from protocol state manipulation to achieve low latency and high bandwidth in MAGIC. The protocol state manipulation is done by a macropipeline made up of three functional blocks - Inbox, PP, and Outbox. The data is copied once into a staging area called DB which contains sixteen data buffers, each large enough to store one cache line. Thus, the architectural definition also defined the functional partitioning of MAGIC, which consists of eight major functional blocks: NI, PI, MC, IO, Inbox, PP, Outbox and DB.

The functional blocks of MAGIC were assigned to one of six designers for implementation. Hardware description languages such as Verilog HDL or VHDL [18, 19] provide a platform for describing and simulating hardware in register-transfer logic (RTL) format. Alternatively, designers can begin with a higher-level description of a design using a programming language such as C or C++ [20, 21]. CAD tools are available for synthesizing such high-level descriptions into register-transfer logic (RTL) format described in Verilog or VHDL [22, 23, 24, 25, 26]. High-level synthesis tools schedule and bind high-level operations to resources by making trade-offs between the latency in number of clock cycles and the area of well-characterized structures, such as memories and arithmetic operations. These tools are highly effective for designing graphics and DSP systems that require converting data-manipulation algorithms, typically consisting of loops, into datapath-intensive hardware. However, for the functional blocks of MAGIC, mainly consisting of state machines that communicate with well-specified interfaces, the design challenge was not in picking the right way to implement a functionality from several different ways. Rather, the challenge was to interpret the requirements of the different interfaces and to synchronize the exchange of information between them in terms of timing and format. Hence, we designed the functional blocks of MAGIC using Verilog.

We described the *RTL* of all the functional blocks of MAGIC in behavioral *Verilog*, with a few structural instantiations for large datapath modules and memories. I was responsible for designing the *IO* interface. The design of my block, as all the remaining blocks, began with understanding the functional specification of all input/output interfaces - namely the PCI bus protocol, communicating headers with *Inbox* and *Outbox*, and exchanging data with *DB*. This understanding determined the datapaths, state-machines and other random-logic I needed to implement to exchange information between MAGIC and *PCI* bus by responding to MAGIC messages and *PCI* commands, while managing common resources in *IO*. Since the designers developed all blocks on the chip concurrently, the implementation of *IO* evolved with changes in the interfaces of *Inbox*, *Outbox* and *DB*.

While RTL development was in progress, we did chip-level planning determined the high-level look of the chip layout.

#### 2.1.1 Chip-level Planning

Once the primary input/outputs of the chip as well as the input/outputs of all functional blocks were known, we decided locations of primary input/output pins of MAGIC as well as of each functional block. This led to a chip-level floorplan of the functional blocks. The floorplan was updated each time new implementation details about the functional blocks were made available through implementation of more functionality in the RTL.

For chips with many functional blocks each interfacing with many other functional blocks, RTL planning tools are available for chip-level planning to determine the relative placement of the blocks that gives the best area and timing. RTL planning derives the area, wire-load and timing constraints on the boundaries of functional blocks, and even improves on the functional partitioning to reduce the amount of global wiring on the chip [27, 28, 29]. The logic inside each block is roughly mapped to pre-characterized instances to estimate the area and timing of the block. Chip-level trade-offs are made between the area, timing and locations of different functional blocks to ensure that all blocks fit on the chip and meet the chip-level timing

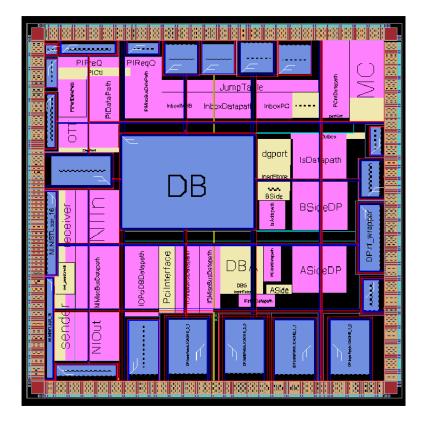

Figure 2.2: Floorplan of MAGIC

constraints. These trade-offs are made by iterating automatic floorplanning, global wire-routing and timing analysis tools [30, 31, 32, 33],

The floorplan of MAGIC is shown in Figure 2.2, where memories are shaded dark and functional blocks are shaded lighter. The memories have pre-determined size and geometries, making them hard macros. The rest of the logic is made up of soft macros with sizes and geometries that were determined by the floorplanner. The fabrication technology put several constraints on the placement of hard macros. Large designs with such constraints in the floorplan are not handled well by the floorplanning tool of the layout system used for MAGIC. Therefore, we manually floorplanned the chip. Each designer periodically synthesized their partially implemented blocks into logic gates to keep track of their latest size and timing characteristics. The timing constraints and capacitive loading of global nets on the boundaries of the major functional blocks were determined by iterating chip-level floorplanning with manual

exchange of block-level timing requirements between the designers.

These area, timing and wire-load characterization on the input/outputs of functional blocks were used to derive gate-level implementation constraints on the boundaries of each block.

#### 2.1.2 Gate-level Implementation

Using the timing constraints and wire-loads of global nets derived by chip-level planning, the mostly behavioral RTL description of each functional block was converted to detailed gate-level implementation by each designer. It is common practice to use module compilers for non-critical or well-known datapath and memory modules [34, 35] and to use manual design for datapath or memory modules with aggressive performance targets to take advantage of circuit design techniques [36], [37]. Blocks with large regular structures such as the PP instruction cache, internal memories used in NI, PI and Inbox, and two 64-bit wide integer datapaths of the PP were designed using LSI's datapath and memory compiler tools. Since the DB had many read/write ports and was critical to achieving MAGIC's performance target of 100MHz clock-cycle, its circuit-level implementation was designed manually by two designers through iterations between circuit design, block-level floorplan, and HSpice simulations. In Figure 2.2, datapaths designed using the LSI datapath compiler are shaded darker than random-logic blocks. The regularity of logic makes manual design of datapaths and memories feasible. On the other hand random-logic blocks, describing state machines and other control logic, were designed using automatic logic synthesis [38] and layout [39], [40], [41] tools.

While logic synthesis converts the RTL description of a random-logic block into gates from a standard-cell library, layout decides the physical placement of these gates and routes nets that connect them. Standard-cell libraries give several implementations of logic gates and regular structures with pre-characterized parameters, such as timing, input loading, and output drive. We used LSI Design's  $0.5\mu m$  standard-cell library lcb500K along with Cmde and SILO tool suits [41] for layout, and Synopsys  $Design\ Compiler\ [38]$  for logic synthesis of MAGIC's random-logic blocks. The logic

of each functional block was further partitioned into sub-modules by its designer for design readability and faster run-times during synthesis. Since the actual wire-load of nets was not known during logic synthesis, the post-layout wire-load of nets was predicted using models based on empirical data from previous layouts and the netlist structure. Synthesis was repeated with refined wire-load models derived from the latest layout until the layout of the block met its timing and area constraints.

The design flow of the MAGIC chip shows that each stage of the chip-design process iterates between logical and physical design. This is due to the fact that picking the correct logical structure depends on the physical topology but the physical topology changes with changing logical structures. As the design moves to lower levels of abstraction, the number of iterations increase since there are more components with unknown locations and logical structures. The next section focuses on iterations between gate-level logic synthesis and cell placement done in the conventional design flow at the lowest level of abstraction.

### 2.2 Conventional Design Flow

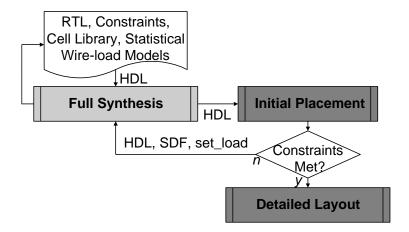

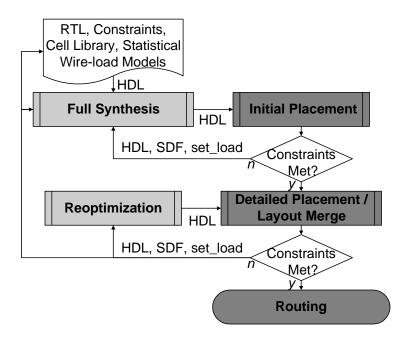

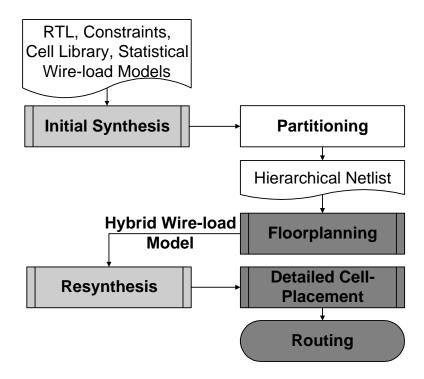

The conventional flow for standard-cell based design of random-logic blocks is shown in Figure 2.3. This flow was widely used until 1998, and is being augmented and often replaced by new flows proposed recently [12, 10, 42, 43, 39, 44, 8, 9]. The flow starts with a standard-cell library and corresponding wire-load models, and with the *RTL* description, area constraints and timing constraints of a design. The steps performed by a logic synthesis tool are shaded light and those performed by a layout tool are shaded dark.

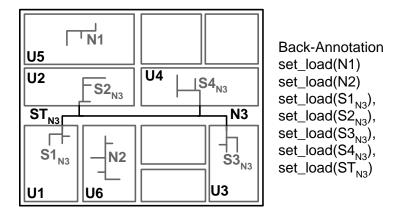

The two tools communicate information through data files that follow standard formats. The input to the first logic synthesis step is a hardware-description language (HDL) file, describing the behavioral RTL of the design. Synthesis optimizes the design netlist and generates another HDL file with a gate-level RTL description. The layout tool determines rough initial placements of these gates. If the design does not meet timing constraints after placement, full synthesis is repeated using physical information from layout which is back-annotated on the netlist through set\_load and

Figure 2.3: Conventional Methodology

SDF files. The set\_load file gives the capacitive load of each net and the standard delay format (SDF) file gives delays through each gate and net segment. Iterations between full synthesis and initial placement continue in this manner until timing constraints are met after the initial placement, when the flow proceeds forward to detailed layout.

Both synthesis and layout tools use static-timing analysis to calculate delays in the design, both for generating SDF reports at the end of each step, and for identifying timing-critical portions of the design during optimizations within the tool.

### 2.2.1 Static Timing Analysis

Static timing analysis [45, 46] traverses the netlist graph twice in reverse topological order [47, 48] to calculate the latest arrival time and the earliest required time of each node in the netlist graph. A netlist graph consists of nodes representing gate pins and primary input/output pins of the design, and of edges representing interconnections of those nodes. Timing constraints on the primary input/outputs of the design and the desired clock speed are used to calculate the timing slack of each node, which is the difference between the required signal arrival time and the worst-case actual arrival time of the node. Nodes with negative timing slack are critical, because they violate the timing constraints of the design. Primary inputs and data outputs of synchronous logic elements such as flip-flops and latches are timing sources, whereas

primary outputs and data inputs of synchronous logic elements are timing sinks. Timing paths go from timing sources to sinks, and have timing slack equal to the slack of the sink node. Timing paths with negative timing slack are called critical paths. The most critical path decides the maximum speed at which the design can be clocked. Both synthesis and layout tools give higher priority to optimizing the timing of critical paths even at the expense of some area increase, and recover area from other non-critical parts of the netlist. Thus, it is very important for synthesis to have an accurate notion, not only of the worst critical paths of the netlist, but also of the relative criticality of paths in order to pick the right logic for timing optimizations.

During static timing analysis, gate delays are derived using pre-characterized timing information from the standard-cell library, which depends on the parasitic loading at the output of each gate. Wire-delays, as well as the output loading of each gate, are derived from the parasitic loading of wires in the design. Determining wire-loads in a layout is a matter of interpreting the physical information already available. However, wire-loads need to be estimated for timing-analysis during synthesis since the gate locations and the wire-routes are unknown. Thus, the accuracy of timing analysis during synthesis depends on the accuracy of its wire-load estimates. The next section describes wire-load estimation techniques for logic synthesis.

#### 2.2.2 Wire-load Estimation

Before any layout is done, statistical wire-load models, provided by the standard-cell library, are used to estimate net-lengths during synthesis. Statistical wire-load models characterize all nets with the same fanout count by the same wire-load capacitance. The model provided by standard-cell library vendors is derived from the statistical distribution of post-layout wire-loads of nets in previous designs that have similar area and are based on the same library and technology. This model usually represents the median of the distribution for each fanout.

After initial layout is done, the actual wire-loads of nets are back-annotated to logic synthesis, allowing synthesis to re-optimize the netlist with more accurate wire-load models. Custom statistical wire-load models are derived from the statistical

distribution of wire-loads back-annotated from the latest layout of the design. Custom models are more accurate than library-provided statistical models, since the data used to derive the model represents the size, aspect ratio, and type of netlist connectivity of the design. Such models are refined further by trimming a small percentage of all nets from the top and bottom of the wire-load distribution in order to ignore outliers. Another refinement makes the model more conservative by picking a wire-load number that represents higher than the 50 percentile point in the distribution for each fanout. However, the inherent limitation of all statistical models is that all nets with the same fanout are represented by one number.

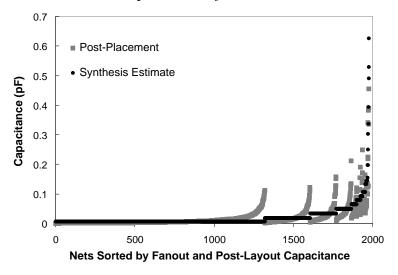

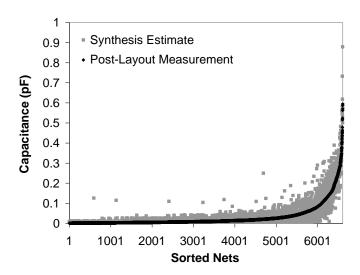

Figure 2.4: Limitation of Statistical Wire-Load Models

Figure 2.4 illustrates the error in wire-load estimation when a custom statistical model was used for all internal nets of a 7K-gate design in a  $0.5\mu m$  technology. The figure compares the post-placement wire-load of nets, shaded light, with the corresponding custom wire-load estimate used by full synthesis, shaded dark. Points on the x-axis represent nets sorted by increasing fanout and then by post-placement wire-load capacitance. It is evident here that the post-placement wire-load capacitance has a wide distribution for each fanout, which is modeled by one number. Even though the wire-load of 80% short and medium-length nets is estimated either conservatively or accurately, the longest 20% nets are highly underestimated.

Two techniques have been proposed for estimating wire-loads using parameters

derived from the netlist structure [49, 50]. These techniques analyze the fanin and fanout cones of nets, to sort them by expected wire-load capacitances. Nets are separated into short, medium and long categories. This enables piece-wise linear modeling of the wire-load distribution in a design using a different statistical model for each of the three categories. These models are more accurate than fanout-based models, because each category is modeled separately within a given fanout. However, due to the steep tail of wire-load distribution for each fanout seen in Figure 2.4, these models are also inaccurate for long nets even though the estimation errors are lower than fanout-based models.

Statistical wire-load models are used by the full synthesis step in the flow of Figure 2.3. The next section describes this step.

#### 2.2.3 Full Synthesis

A logic synthesis tool parses the RTL of a netlist and applies Boolean and algebraic transformations to minimize its logic [51], [52]. The netlist is usually represented in an internal graph format, where primary input/output pins as well as Boolean logic expressions make up the nodes of this graph, whereas interconnections between nodes make up the edges. Technology mapping maps this graph to gates from the standard-cell library being used, while meeting the area and timing constraints of the design.

Technology mapping partitions the netlist graph into smaller cones of logic and matches these cones against graphs representing library cells. Dynamic programming is used to pick the best set of graph matches that meet the area constraints while minimizing the delay through the design. The timing analysis uses statistical wire-load models given by the library or custom models derived from earlier layout to estimate wire-lengths of nets that connect the logic cones. The minimum unit of optimization here is a small logic cone, typically similar to the size of a few basic logic gates. Since this is the technology-dependent portion of synthesis optimizations, it is most susceptible to inaccuracies in wire-load estimates. Later in this thesis, we will look at peer research combining technology mapping with layout, and our work will

increase the size of the smallest optimization unit of this step to a larger cluster of gates in a new design flow.

Technology mapping creates gate-level representation of the design, which is sent to the layout tool for initial cell-placement in Figure 2.3.

#### 2.2.4 Initial Cell-Placement

The gate-level description generated by logic synthesis is converted to the lowest level description in terms of silicon layers by an automatic layout tool [31, 53]. Initial cell-placement decides the relative placement of all gates. In order to meet the total area constraint and the timing constraints, the total length of interconnections between gates is minimized. Interconnection lengths between timing-critical gates are minimized while non-critical gates are placed to minimize the area. Constructive cell placement algorithms are used to give the initial locations of gates. Such algorithms determine relative locations of all interconnected gates close to one another [54, 55, 56], although these locations could be overlapping. Since the nets are not routed at this stage, wire-lengths are estimated using the placement of their pins. These estimates are used to derive placement cost functions, such as total interconnect length, and to perform static timing analysis.

The wire-length of a net can be roughly estimated as the half-perimeter of the bounding box enclosing all pins of the net [57]. While this estimate is fairly accurate for nets with three or fewer pins, a more accurate estimate is needed for higher fanouts. Higher fanout nets can be estimated accurately by drawing a spanning tree that connects all of its pins once [58]. A spanning tree estimates a realistic route of the net, while ignoring the effect of other nets and of the potential area congestion that could alter the actual routing.

After initial placement, static timing analysis gives more accurate timing information about the design compared to the timing estimated by full synthesis. Due to the inaccuracy of statistical wire-load models used by full synthesis 2.4, a design that meets timing constraints after full synthesis does not always meet timing constraints after initial placement. In that case a custom statistical wire-load model is derived

by back-annotating net-lengths extracted from initial placement. Full synthesis is repeated with the custom wire-load model, followed by another pass through the initial placer. Neither full synthesis nor initial placement use the output of the previous pass of the tool as an initial solution, rather they start from scratch each time. Hence, both are unable to preserve the wire-load model used by earlier passes. Such non-incremental iterations between full synthesis and initial placement are repeated until the design meets timing constraints after initial placement, when it is taken to the detailed cell-placement step.

#### 2.2.5 Detailed Cell-Placement

Detailed placement takes the rough initial placement as a seed solution and optimizes it further by using a corrective placement tool. Corrective placement algorithms use random cell movements to improve this rough initial placement for a given objective function such as area or total length of interconnections or both [54, 59], while ensuring legal (non-overlapping) locations for all gates. Cells in a standard-cell library usually have the same height but different widths, so legal cell placement consists of rows of uniform height cells separated by channels of space kept open for routing. Significant changes are made to the initial placement, changing the wire-lengths of several nets. Since constructive placers use random algorithms, the fanout-based custom wire-load model used by full synthesis can not predict these changes in wire-lengths.

The longest nets with underestimated wire-loads, which appear in the tail of the wire-load distribution for each fanout in Figure 2.4, affect design convergence in several ways. Synthesis picks the wrong logic structure to drive such a net, resulting in insufficient drive after placement. Since timing is a worst-case metric, such nets end up on critical paths after placement. Also, synthesis has the wrong notion of relative criticality of paths. Hence, placement may reveal new critical paths that are not well optimized for timing, whereas other relatively non-critical paths may be unnecessarily optimized by synthesis. The post-placement timing of the design may have higher worst-case delay, more critical paths in violation of the timing constraint,

and some non-critical logic that has been over-optimized by synthesis. Thus, even if the design met timing after initial placement, there is no guarantee that the timing would be met after detailed placement.

Sylvester and Keutzer show that the delay of medium-length wires is not likely to increase in comparison to gate-delay as technology scales, hence the impact of such wires on design timing is not likely to increase [60]. However, Ho et al. [61] predict an increase in the number of long wires on a chip as well as in each module as higher integration will motivate synthesizing larger design blocks to manage chip complexity. They also show that as technology scales, long wires will have increasing impact on design timing since an average library gate will be able to drive shorter and shorter wires before the wire-delay becomes a significant fraction of the gate delay. This will make the tails of the wire-load distribution, such as the one shown in Figure 2.4, even longer; escalating the problems created by the inaccuracy of statistical wire-load estimation.

Timing-driven placement algorithms use static-timing analysis to sort gates and nets in the design by the relative criticality of timing paths going through them. Higher preference is given to optimizing the layout of more critical gates and nets in this list [62], [63]. Such algorithms refine the cost function of placement algorithms by introducing critical-path timing information in it, but they do not help design convergence in this flow. This is due to the fact that the relative criticality of gates and nets is not updated while changes are begin made to the layout. Hence, timing-driven layout algorithms also suffer from the problem of estimating the timing too early and not keeping it consistent with the latest layout.

Thus, more logic synthesis is required to fix timing violations of new critical paths that appear after detailed placement.

### 2.2.6 Reoptimization and Layout-Merge

The design flow of Figure 2.3 needs to be extended in order to fix critical paths appearing after detailed placement due to inaccurate wire-load estimation during earlier synthesis. This extended flow is shown in Figure 2.5. The reoptimization

Figure 2.5: Conventional Methodology with Post-Layout Optimizations

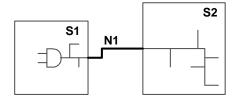

step performs limited synthesis transforms to fix timing violations while preserving the layout that was committed thus far. Such transforms consist of driver sizing, buffer/inverter insertion and re-structuring of logic along timing-critical paths. Recent research on these and other post-layout timing-optimization techniques will be discussed in Chapter 3. Accurate wire-loads derived from estimated routes in detailed placement are back-annotated to synthesis, hence the initial timing analysis during reoptimization gives accurate timing information corresponding to the current layout. Back-annotated wire-loads are maintained on all nets with no changes or in-place changes in their fanin or fanout logic. In-place changes typically consist of exchanging gates in synthesis that can be similarly exchanged in layout because the two gates have the same physical footprint. This is usually done when a gate is replaced by a different drive-strength implementation of the same logic gate. However, nets with changed logic on their fanin or fanout are represented by a custom wire-load model derived from the initial back-annotation, since synthesis does not know where the new gates will be placed.

Netlist changes made by reoptimization are merged with the existing placement in

the layout-merge step, using an engineering change order (ECO) placement tool that performs incremental layout [64], [65]. ECO placers nudge cells around their original locations to accommodate new or upsized cells. The successful implementation of an ECO depends on the number and amount of changes attempted, and also depends on the area-utilization of the original placement. Often the addition of many new gates and fragmentation of layout area requires random placement of previously placed gates, which nullifies the wire-load back-annotation used by reoptimization to pick its transforms. Hence, maintaining incremental layout changes limits the amount of optimizations that can be allowed during reoptimization.

Iterations between reoptimization and layout-merge are repeated until the layout meets timing constraints, at which point it is sent for wire-routing. Timing problems discovered after routing are usually fixed by in-place sizing and manual buffer insertions, since the amount of detail committed in layout does not allow for significant changes in the netlist.

This design flow has an unfortunate property; as more accurate information becomes available through increasing detail in layout, less freedom is available in synthesis to use it. Reoptimization is very effective in pruning out timing problems by making small changes to the netlist at a late stage in the design cycle. However, in tightly constrained designs such limited optimizations are not sufficient to fix timing problems that are created due to wrong logic structures picked by earlier full synthesis. Netlist-level granularity of tool iterations, inaccuracy of statistical wire-load models and non-incremental nature of layout tools result in an inconsistent view of wire-loads between synthesis and placement throughout this flow. Hence, there is no guarantee that one iteration in Figure 2.5 will give better timing than the previous one. When these iterations do not converge, either the design is taken to a previous stage of the flow, or the designer manually makes changes to the layout or the netlist in order to arrive at the final design implementation. Either of the two solutions costs a large amount of designer effort and time.

Addressing the limitations of this methodology has been an active area of research in recent years. The next chapter covers related research in the area of bridging the gap in the wire-loads and timing viewed by synthesis and layout.

## Chapter 3

# Bridging the Gap Between Synthesis & Layout

Deep-submicron fabrication technologies have led to the integration of entire system-on-chip (SoC), with several millions of gates and aggressive performance targets. Shrinking device sizes and increasing chip complexity has led to new design challenges such as controlling power dissipation, maintaining signal integrity along long wires, and achieving high performance. All of these tasks must be completed in short time-to-market schedules in order to be competitive. Increasing design complexity directly translates into increasing requirements on design automation tools. CAD techniques, for predictable convergence to an implementation that meets the design's constraints, have been a topic of active research in recent years.

A CAD flow is convergent if the design meets its constraints, such as area, timing, power dissipation, signal integrity rules, etc., within a known maximum number of iterations. If the design constraints are too tight, an implementation that meets all constraints may not exist, or may not be achievable in a given CAD flow. In such cases, the CAD flow is convergent if, within a known maximum number of iterations, it arrives at a best-effort (not necessarily optimal) design implementation with some constraint violations. Such designs would require relaxing some of the design constraints, in order to meet time-to-market constraints. Our work focuses on timing convergence, which is the problem of design convergence restricted to two

conflicting constraints: timing and area. Chapter 2 showed that the conventional CAD flow lacks timing convergence since there is no upper bound on the number of netlist-level design iterations needed before design constraints are met, or before it is known that future iterations would not improve constraint violations. This chapter presents related research which addresses this problem, and the next chapter presents our approach.

Keutzer et al. [66] described the impact of deep-submicron technology on large scale designs, and on the future of the design automation methodology. While their paper does not describe implementation details, it does propose various high-level alternatives for tighter interaction between synthesis and physical design that fall into three categories: synthesis-driven layout, layout-driven synthesis, and simultaneous synthesis and layout. Research work in these three areas is described in Sections 3.1-3.3. Synthesis-driven layout takes a radical approach where synthesis drives the layout instead of estimating its outcome. Layout-driven synthesis techniques make incremental optimizations to the netlist topology and layout, thus improving the implementation generated by earlier passes of synthesis and layout tools. Simultaneous synthesis and layout techniques iterate low-level synthesis and layout transforms in an incremental fashion, while keeping a consistent view of wire-loads and timing between the two and creating a convergent optimization flow. The discussion involving related research leads to our view of the ideal optimization flow that merges synthesis and layout in one integrated tool.

#### 3.1 Synthesis-driven Layout

Synthesis-driven layout techniques budget the timing of the design during logic synthesis. These timing budgets serve as constraints that the layout tool is required to meet through placement and sizing. Instead of predicting post-layout wire-loads during synthesis, synthesis-driven layout makes the layout obey cell-delay and wire-length assumptions made by synthesis. This approach has the potential for creating a forward-only methodology that does not require iterations between synthesis and layout.

25

A synthesis-driven layout methodology, based on wire-planning during logic synthesis, is being developed by Brayton et al. [67], [68], [11]. In wire-planning, logic synthesis distributes delay among global wires and functional blocks at the chip-level and among gates and local wires at the block-level. Block-level synthesis produces a netlist with region-based gate-placement constraints. Synthesis optimizes the netlist, using timing information derived from the assumption that the layout will meet its gate-placement constraints. The placement constraints ensure that every path from a primary input to a primary output of the block are no longer than the Manhattan distance between its endpoints, which enables simple but accurate wire-load modeling during synthesis. The placement engine has to meet the gate-placement constraints, but is free to pick gate sizes in order to meet corresponding gate-delay budgets assumed by synthesis. This is enabled by a cell-library that has many different sizes for each logic gate.

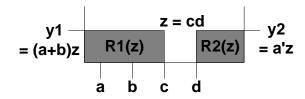

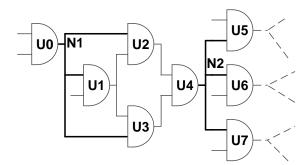

Figure 3.1: Example of Duplications Required in Wireplanning

However, if a node is in the fanin cone of two paths going in opposite directions, it has to be duplicated to ensure Manhattan lengths for both paths. This is shown in the example of Figure 3.1. Here, node z belongs to the fanin cones of two primary outputs y1 and y2. In order to ensure that the path from c to y1 is not longer than the Manhattan distance from c to y1, z should to be placed within region R1(z). Similarly, for the path from d to y2, z should be placed in region R2(z). Since R1 and R2 are non-overlapping, z needs to be duplicated. Due to such duplications, wire-planning suffers from exponential area overheads even in small designs. Its applicability will depend on future work done to address this limitation.

Magma Design Automation [12] is a startup company that has taken a similar approach. This approach is based on the work by Brand *et al.* [69] which proposed that synthesis should be done to guarantee a performance target, and that layout can

meet the same target if continuous gate-sizes are available. Magma's Fixed Timing methodology uses a common netlist database and static timing analyzer for both synthesis and layout algorithms. Their methodology freezes the timing of the design during synthesis using logical effort [70] to estimate and budget post-layout timing. The netlist is mapped to "superCells" that represent the functional implementation of the logic with constant delay but variable area. Next, their placement tool performs sizing, buffer insertion, and logic restructuring; along with placement; in order to maintain gate-delay budgets by matching gate sizes to their output load. The sizes of non-critical superCells are reduced to make room for increase in the sizes of critical superCells during placement. However, logical effort does not model wire-delays that are significant in large designs and that also change with wire-length changes caused by resizing superCells in the fanout of long wires. Due to this, it is unclear whether this methodology scales effectively to large designs. In our opinion, the effectiveness of this methodology depends on the placement engine's ability to find avenues for making sizing trade-offs that keep the design area reasonably low, while incorporating changes in delay budgets due to logic restructuring and buffering.

#### 3.2 Layout-driven Synthesis

As seen in Section 2.2.6, reoptimization and layout-merge are important steps for narrowing the gap between synthesis and layout timing in the conventional methodology. Research in layout-driven synthesis (also referred to as post-layout optimization) techniques focuses on improving the effectiveness of these steps. These techniques make local changes to the netlist or the layout using transforms that target a few of the worst critical paths; based on accurate wire-load and timing information available after layout. As discussed in Section 2.2.6, the scope of such transforms is limited by the ability of the layout tool to incrementally merge netlist changes without significantly perturbing unchanged portions. Moreover, converging to timing improvements through the application of these transforms also depends on the accuracy of its timing analysis engine. Section 3.2.1 describes the impact of timing analysis on the effectiveness of layout-driven synthesis transforms. Sections 3.2.2-3.2.3 describe the

research in layout-driven synthesis heuristics, divided in three categories based on their target optimization space: buffering and sizing transforms improve the drive on heavily-loaded nets; relocation and re-wiring transforms shorten either net-lengths or logic depth along critical paths; and logic re-structuring transforms resynthesize critical logic to improve timing. The techniques presented here fit very well into the conventional CAD flow, and are incorporated in most commercial CAD tools today.

#### 3.2.1 Timing Analysis for Layout-driven Synthesis

Timing analysis is used to choose parts of the netlist for applying a layout-driven synthesis transform. Furthermore, it is used after applying such a transform to accept or reject the changes. More accurate timing analysis is computationally expensive but gives a more convergent flow of post-layout timing optimizations.

The timing analysis engine needs to estimate the capacitive loading of nets on driving gates and the propagation delay of nets. If routing is not done, the length of a net is estimated by less accurate measures, such as half-perimeter of its bounding box [57]; or by more accurate but time consuming measures, such as spanning-tree approximation of its Steiner route [58]. The propagation delay (or RC-delay) is roughly estimated using the product of lumped resistance and capacitance for a given net-length. A more accurate calculation of RC-delay is done by viewing the net as a distributed RC tree, and deriving its Elmore delay [71], [72]. The Elmore delay of a RC network represents the first moment of its impulse response.

Either the timing of the most critical path or several long paths can be considered when choosing a layout-driven synthesis transform. Tightly constrained designs have several timing paths with similar timing, and sharing a lot of logic. Hence, fixing only the worst path may introduce new paths that are also affected by the transforms. A more conservative, but computationally more expensive, approach would consider several of the longest paths when choosing a transform. The complexity of enumerating all paths in a netlist with N nodes is  $O(e^N)$  [47]. Alternatively, only the top K critical paths can be enumerated using the algorithm proposed by Ju and Saleh [73] which also allows for the enumeration to be stopped when a desired max-

imum CPU time is spent. Enumerating a higher number of paths before picking a transform improves the chances of getting timing improvements, without introducing new critical paths.

The granularity of interaction and the consistency of wire-load data, between actual layout and the layout-driven synthesis transform, determines whether the transform converges to timing improvements. Some physical information is lost when the topology or placement of logic on a net is changed. If several netlist or layout changes are made before analyzing post-layout timing, the interaction of different transforms may have a negative impact on the overall timing. A safe, but computationally more expensive, approach would be to accepts only those transforms that improve timing after the layout has been updated for each low-level transform.

Research in layout-driven synthesis techniques, presented below, differ in the type of transforms performed, in the accuracy of timing and wire-load analysis, and in the granularity of netlist modifications made before layout and timing are updated.

#### 3.2.2 Buffering and Sizing

Inserting buffers as repeaters on very long nets is a very effective way of improving the RC delay of a net, while reducing the load seen by the net's driving gate. The technique by Sato et al. [2] derives segmented wire capacitances and resistances from the layout tool, and calculates the Elmore delay of nets for timing analysis [71]. Their technique chooses terminals on the most critical path for buffer insertion on high-fanout nets and for gate sizing. Kannan et al. [3] ignore the RC delay of wires in their timing analysis but derive accurate wire-load capacitances through detailed analysis of the fanout tree of each net. Their technique also chooses nets on the worst critical paths for buffer insertion. The layout has to be able to absorb new buffers in specific locations along a net's route in order to get the benefit of buffer insertion.

Driver sizing improves timing by upsizing those gates that significantly contribute to critical path delay due to excessive capacitive loading on their outputs. Chuang and Hajj [4] calculate the timing slack for all gates using lumped RC models for wires; and they solve a linear program to minimize the slack of critical gates and those directly

connected to them through gate-sizing and relocation. Sizing makes small changes to the layout to accommodate for differences in area of gates with different drive strengths. Usually these are absorbed in the existing layout by nudging neighboring gates away.

Buffering and sizing are inexpensive transforms that improve the drive on heavily-loaded nets, but require small amount of layout merge. Buffering is very effective in pruning out timing problems due to the parasitic loading of long nets. Sizing effectively fixes gate drives on underestimated short to medium length nets. However, their scope is limited. Inserting a buffer on local nets of a block takes up delay and area. This can be avoided if a stronger logic structure is synthesized to drive the net. Sizing is not always possible since only a limited amount of upsizing can be done on a gate before other gates in its fanin cone are overloaded.

#### 3.2.3 Relocation and Re-wiring

Gate relocation moves critical-path gates closer in order to improve timing, by reducing the wire delay along critical paths. Chuang and Hajj [4] use linear programming to derive optimal netlist-level relocations based on timing analysis of the current layout. However, making many relocations at once before analyzing their impact on post-layout timing results in non-incremental layout changes that end up with worse timing. Instead, it would be safer to use a heuristic that interleaves low-level relocation decisions with incremental layout and timing updates.

Marek-Sadowska et al. [74, 5] find equivalent cones of logic in a netlist, and rewire gates along critical paths to bypass unnecessary logic stages. Their technique does slack calculation on all gates and chooses nets on and in the vicinity of the critical path for re-wiring and other transforms. In order to consider the effect on other similar critical paths, they also consider the timing of 5 of the next longest paths going through a net as a secondary objective when choosing the net. This is a convergent technique, since every transform chosen is accepted only if it gives timing improvements after layout merge.

Their paper also shows that post-layout optimizations should be applied before

detailed routing, since it is more difficult to absorb netlist changes through ECO when all the details are already committed in the layout. They show that applying re-wiring and buffer insertion together, followed by gate sizing, gives better timing improvements rather than applying any of the three techniques separately. So far, the different layout-driven synthesis techniques exist as individual tools in commercial layout and synthesis systems. There is no one post-layout optimization tool that takes the advantage of simultaneously applying buffering, sizing, relocation and re-wiring.

#### 3.2.4 Logic Restructuring

Logic re-structuring is more effective for timing improvements than other post-layout optimization techniques due to its wider scope. Post-layout logic restructuring of gates on and close to the critical path is shown to improve timing by Lee et al. [6] and Stenz et al. [7]. Both of these techniques choose logic on and around the most critical path in a design, and re-synthesizes it to improve timing. Computational cost limits the number of critical paths being considered for restructuring. Also, the lack of incremental layout tools limit the amount of logic that can be restructured.

Layout-driven synthesis techniques are very effective in pruning out timing problems at a late stage in the design by making local changes to a design based on accurate physical information. However, these techniques improve timing by making corrective changes at a late stage in the design flow. Tightly constrained designs, with many critical paths that share a lot of logic and that have similar timing, hit the scope limitations of these techniques. Hence, post-layout timing optimizations are not sufficient in fixing the lack of convergence in the conventional methodology.

There is a need for more pro-active approaches earlier in the methodology that can achieve timing convergence by picking the right logic structures to drive the right loads.

#### 3.3 Simultaneous Synthesis and Layout

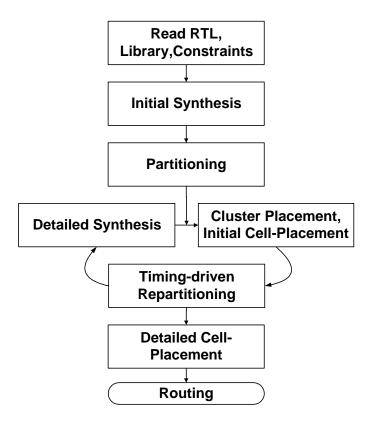

Simultaneous synthesis and layout techniques improve the accuracy of information exchanged and the granularity of optimizations performed by synthesis and layout iterations, creating a more convergent flow starting from first synthesis. Identifying a design flow for simultaneous synthesis and layout, and finding solutions to the challenges involved in developing a CAD system along such a flow, has been the focus of our work as well as of other concurrent efforts including one company and two academic research projects. Monterey Design Systems [10] is a startup company developing a tool for simultaneous synthesis and layout. Their tool is described in more detail in Chapter 4. The two research projects are described in the following subsections.