## PRECISION CMOS RECEIVERS FOR VLSI TESTING APPLICATIONS

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> Daniel K. Weinlader November 2001

© Copyright by Daniel K. Weinlader 2001

All Rights Reserved

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

Mark A. Horowitz Principal Adviser

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

Thomas H. Lee

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

James A. Gasbarro

Approved for the University Committee on Graduate Studies:

# Abstract

Testing CMOS parts is becoming more difficult due to the proliferation of high-speed I/O circuits that operate at frequencies exceeding the performance capabilities of modern testers. The performance gap between high-speed chip I/O frequencies and tester frequencies is further extended by the rapid performance scaling of CMOS, compared to bipolar and GaAs technologies which are commonly used in tester electronics. Furthermore, as VLSI parts integrate increased amounts of functionality and become more complex, testing of the parts becomes more difficult due to insufficient observability of the high-speed interactions between circuits within the chip. Integrating high-speed test capabilities onto production die would permit testing of parts incorporating high-frequency I/O in addition to increasing the observability of internal signals on the die.

The key challenge is to achieve high-precision timing measurements using a process technology that may be no better than the one used to build the part being tested. To overcome the frequency limitations of the process technology, an oversampled receiver with time-interleaved samplers clocked by a multi-phase clock generator is utilized. While this enables a high receiver sample rate, sampler input offsets and static phase spacing errors in the clocks limit timing accuracy. This dissertation presents techniques to measure and compensate for static errors in both the clock generator and input samplers. In addition to static errors, jitter in the clock generator can significantly degrade timing accuracy. Therefore, a technique that measures and subtracts jitter from the timing measurements is proposed.

The aforementioned techniques enable the construction of an input receiver with timing accuracy suitable for testing applications and are demonstrated with a 0.25µm CMOS test chip. Techniques are also presented to integrate a small oversampling receiver onto VLSI parts to increase observability and enable timing measurements of internal signals.

# Acknowledgments

"Art is I; science is we." - Claude Bernard

While this work solely bears my name as the author, it is actually the result of efforts on the part of many people.

This work would not have been possible without the guidance and wisdom of my advisor, Mark Horowitz. He has been both generous with his time and patient and as a result, I have benefitted greatly from my interactions with him. A large part of this thesis is based on work by students who preceded me, Stefanous Sidiropolous, Chih-Kong Ken Yang, John Maneatis and Jim Gasbarro. I can only hope future students will find this work as beneficial. I have been fortunate to work with many wonderful people including, Ken Mai, Bharadwaj Amrutur, James Smith and Gu-Yeon Wei. They have made my research more productive and my time spend at Stanford enjoyable. Ron Ho deserves special mention, not only as a good friend, but for all his help in construction of the test chip. He spent countless hours with unselfish dedication, certainly more than anyone could or should ask of a friend.

While the research and researchers are the primary focus of attention at Stanford, there are a great number of support people who make the work possible. Those who I have had the privilege of working with include Darlene Hadding, Deborah Harber, Charlie Orgish and Joe Little.

My parents taught me the importance of dedication, perseverance, and work ethic, and as a result, my dissertation is a product of their efforts as much as it is of mine. My brother, John, and sister, Karen, have provided me with much support and encouragement.

This work has required a great deal of patience, support and love from my wife, Terese, for which I am eternally grateful. My son Nolan and daughter Audrey have, truth be told, hindered more than helped the completion of this work, but they give new purpose to everything I do and therefore I would be remiss not to mention them.

# Contents

| Abstract                                         | v   |

|--------------------------------------------------|-----|

| Acknowledgements                                 | vii |

| List of Figures                                  | xi  |

| Chapter 1: Introduction                          | 1   |

| 1.1 Test Overview                                |     |

| 1.2 Goals                                        | 4   |

| 1.2.1 Organization                               | 4   |

| Chapter 2: Background                            | 5   |

| 2.1 The Allure of CMOS                           | 5   |

| 2.2 I/O Channel Requirements                     | 8   |

| 2.3 Timing Performance                           | 10  |

| 2.3.1 Detailed Timing Information                | 11  |

| 2.3.2 Over-Sampling Receiver                     | 12  |

| Chapter 3: Timing Accuracy                       | 15  |

| 3.1 Multi-Phase Clock Generation                 | 15  |

| 3.2 Timing Accuracy                              | 18  |

| 3.3 Static Phase Offsets                         |     |

| 3.3.1 Sources of Static Phase Offset             | 20  |

| 3.3.2 Measurement and Calibration                | 22  |

| 3.4 Deterministic Jitter                         | 24  |

| 3.4.1 Measurement and Compensation               |     |

| 3.5 Input Samplers                               |     |

| 3.6 Summary                                      |     |

| Chapter 4: Implementation and Timing Performance | 33  |

| 4.1 Test Chip                                    |     |

| 4.2 Clock Generation                             | 34  |

| 4.2.1 Basic Elements                             | 34  |

| 4.2.2 Delay-Line Based Clock Generator           | 38  |

| 4.2.3 Ring Oscillator Based Clock Generator      | 41  |

| Adjustable Interpolation                         | 44  |

| Array Layout                                     | 46  |

| 4.2.4 Control Loop Design                        |     |

| 4.2.5 Clock Drivers                              |     |

| 4.2.6 Measured Phase Results                     | 51  |

| 4.2.7 Phase Alignment Considerations             |     |

| Duty Cycle                                       | 56  |

| 4.2.8 Phase Adjustment Summary                   |     |

| 4.2.9 Timing Jitter                              | 57  |

| References                       | 95 |

|----------------------------------|----|

| Appendix A                       | 89 |

| Chapter 6: Conclusion            | 85 |

| 5.4 Conclusion                   | 84 |

| 5.3 Testing the Tester           |    |

| 5.2.3 Edge Filtering             |    |

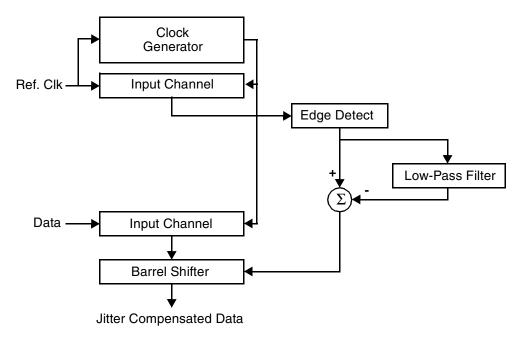

| 5.2.2 Jitter Compensation        |    |

| 5.2.1 Compression and Decimation |    |

| 5.2 Output Data                  |    |

| 5.1 A Minimal Sampling System    |    |

| Chapter 5: Integrated Testing    | 73 |

| 4.5 Summary                      | 71 |

| 4.4 Floorplan                    | 69 |

| 4.3.2 Aperture                   |    |

| 4.3.1 Offset Compensation        |    |

| 4.3 Samplers                     | 63 |

# List of Figures

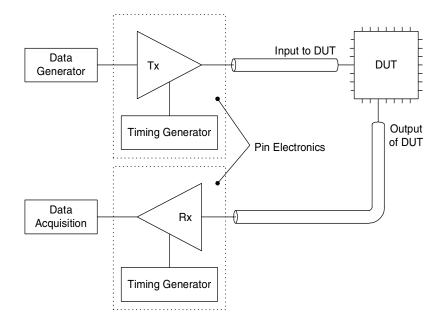

| Figure 1.1: Basic tester architecture                                       | 2  |

|-----------------------------------------------------------------------------|----|

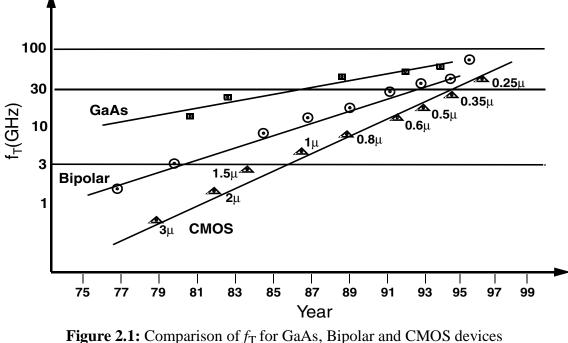

| Figure 2.1: Comparison of f <sub>T</sub> for GaAs, Bipolar and CMOS devices | 6  |

| Figure 2.2: A modern VLSI tester (Teradyne J973)                            | 7  |

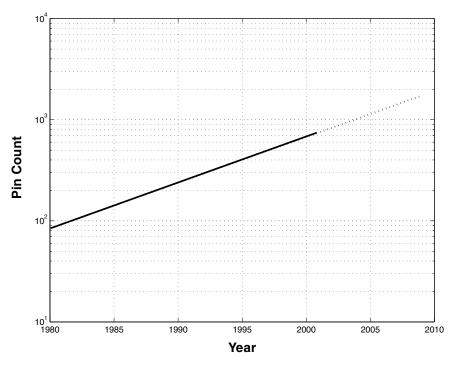

| Figure 2.3: Pin count trends                                                | 8  |

| Figure 2.4: A time digitizer                                                | 11 |

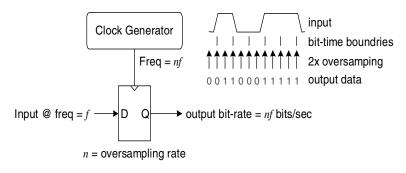

| Figure 2.5: An oversampled receiver                                         | 12 |

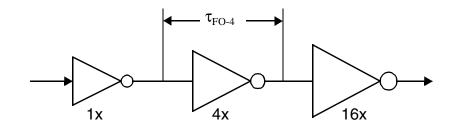

| Figure 2.6: Fanout-of-4 inverter delay                                      | 13 |

| Figure 2.7: A CMOS implementation of an over-sampling receiver              | 13 |

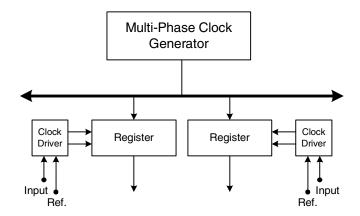

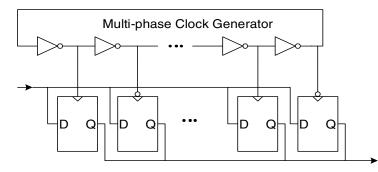

| Figure 3.1: Multi-phase clock generators                                    | 16 |

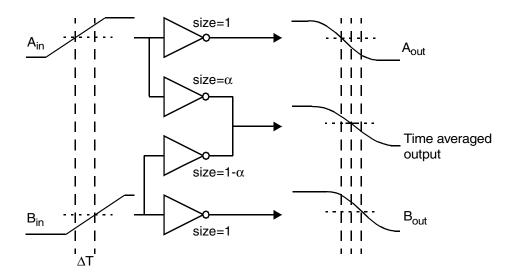

| Figure 3.2: Interpolator operation                                          | 18 |

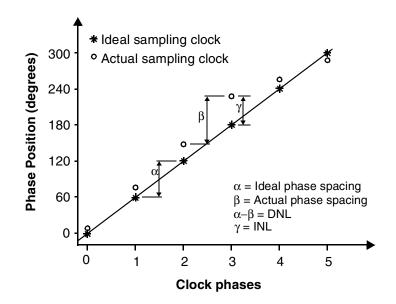

| Figure 3.3: Sample DNL and INL for a six-phase clock generator              | 19 |

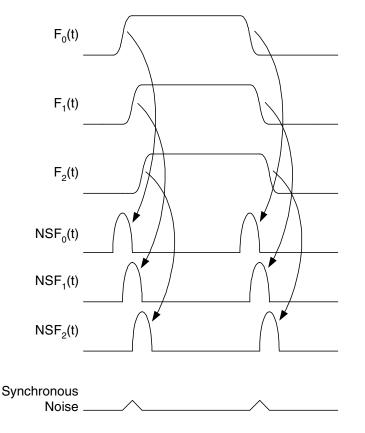

| Figure 3.4: Multiple clock phases and their noise sensitivity functions     | 21 |

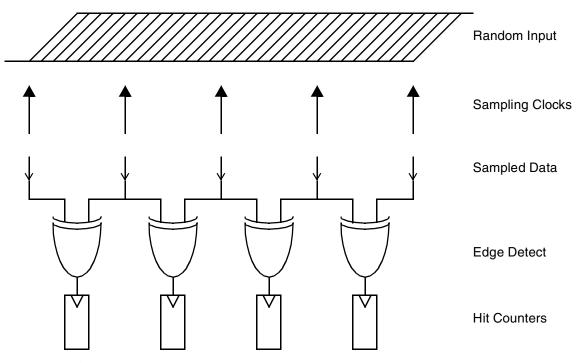

| Figure 3.5: Histogram measurement of static clock phase alignment           | 23 |

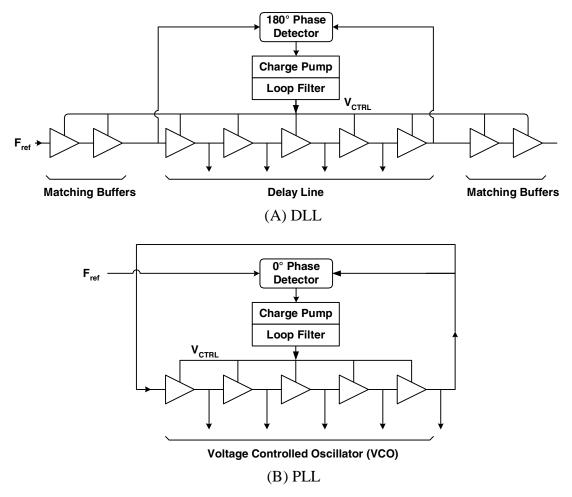

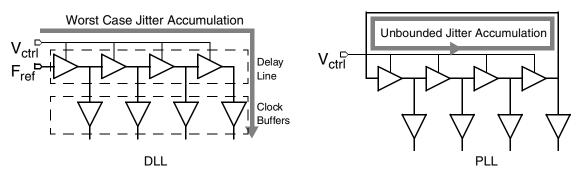

| Figure 3.6: DLL and PLL jitter accumulation                                 | 25 |

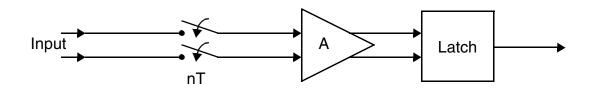

| Figure 3.7: Ideal input sampler                                             | 27 |

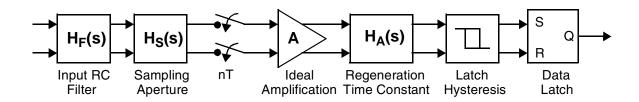

| Figure 3.8: Differential input receiver with non-idealities                 |    |

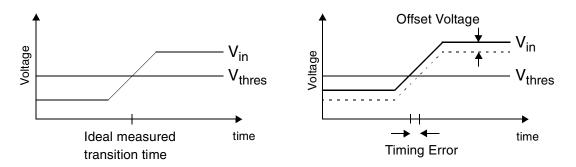

| Figure 3.9: Effect of input offset voltage on timing accuracy               | 30 |

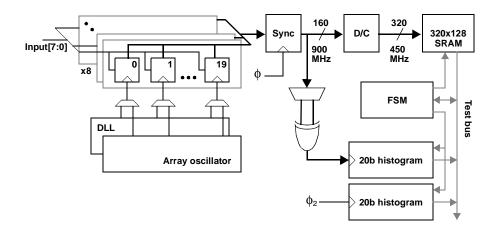

| Figure 4.1: Test chip block diagram                                         | 34 |

| Figure 4.2: Differential delay element                                      | 35 |

| Figure 4.3: Replica bias generator for delay elements                       | 35 |

| Figure 4.4: Differential interpolator                                       | 36 |

| Figure 4.5: An adjustable interpolator with a 3-bit adjustment range        | 37 |

| Figure 4.6: Initial interpolation strategy for DLL                          | 38 |

| Figure 4.7: Interconnect techniques for phase interpolation                 | 39 |

| Figure 4.8: Final DLL interpolation topology                                | 40 |

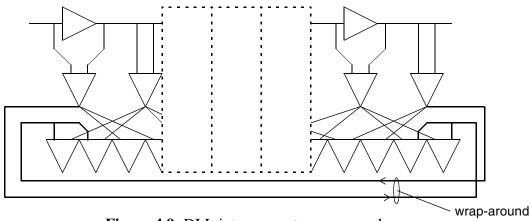

| Figure 4.9: DLL interconnect wrap around                                    | 41 |

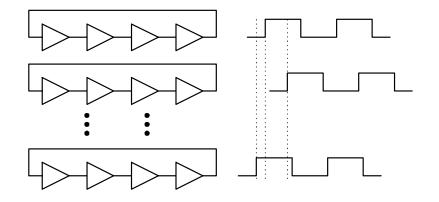

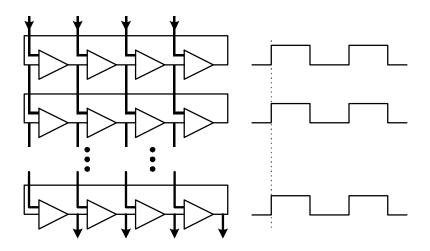

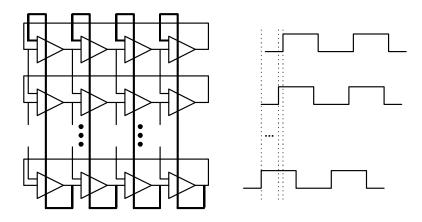

| Figure 4.10: Multiple, uncoupled ring oscillators                           | 42 |

| Figure 4.11: Coupled rings with top and bottom rings uncoupled              | 43 |

| Figure 4.12: Fully interconnected ring oscillators                          | 43 |

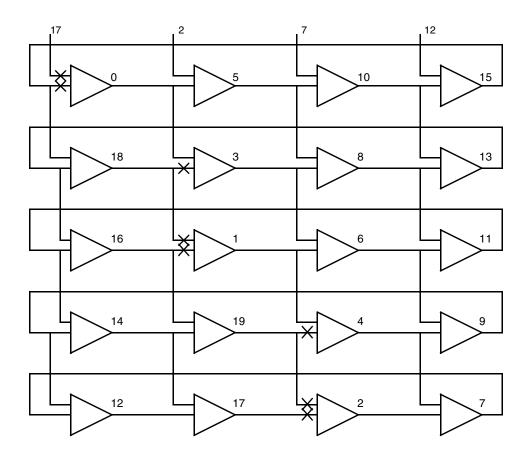

| Figure 4.13: Four by five array oscillator                                  | 44 |

|-----------------------------------------------------------------------------|----|

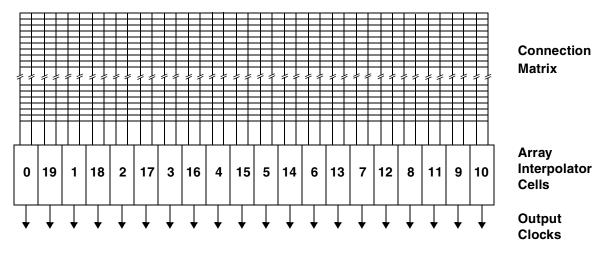

| Figure 4.14: Array oscillator layout                                        | 46 |

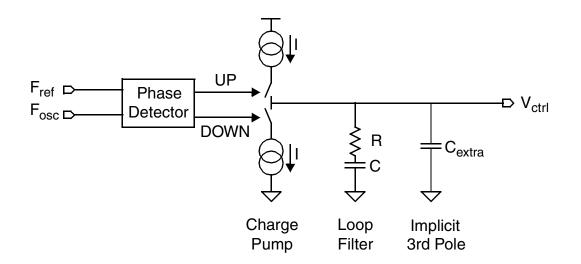

| Figure 4.15: PLL control loop                                               | 47 |

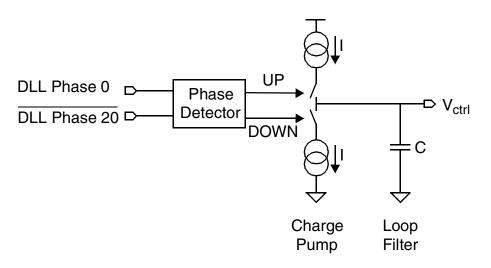

| Figure 4.16: DLL control loop                                               | 48 |

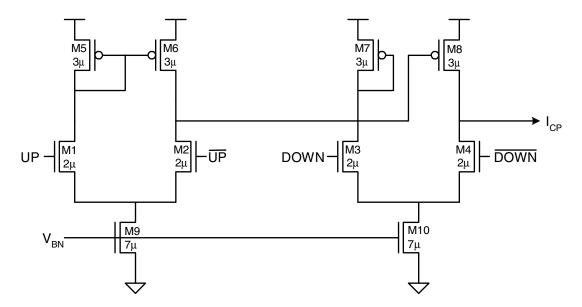

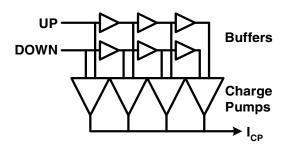

| Figure 4.17: Control loop charge pump                                       | 49 |

| Figure 4.18: Reduced ripple charge pump                                     | 50 |

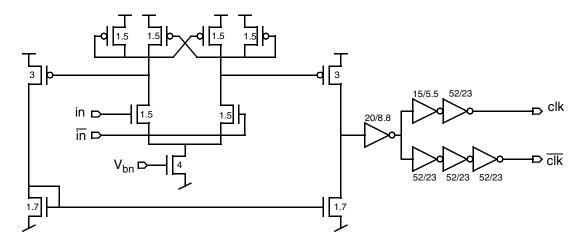

| Figure 4.19: Low-to-high swing converter and clock buffers                  | 51 |

| Figure 4.20: Architecture for histogram measurements of phase offsets       | 52 |

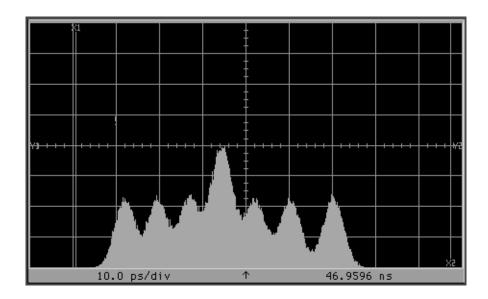

| Figure 4.21: Histogram plot of interpolator output                          | 53 |

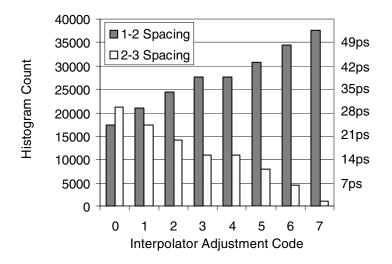

| Figure 4.22: Correlation of histogram measurements to phase spacing         | 54 |

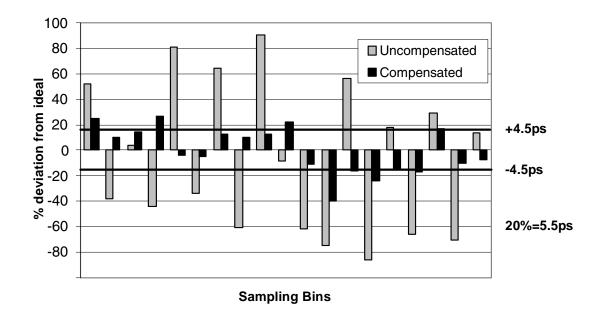

| Figure 4.23: Compensated DLL phase spacing                                  | 55 |

| Figure 4.24: Adjustable timing vernier with buffer delay range              | 56 |

| Figure 4.25: Low-swing constant current output driver                       | 58 |

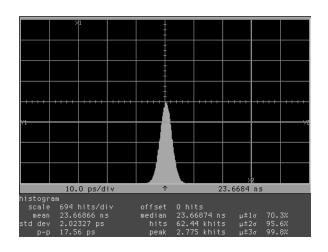

| Figure 4.26: Timing jitter with no induced noise                            | 59 |

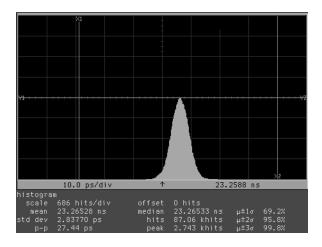

| Figure 4.27: Timing jitter with induced noise                               | 60 |

| Figure 4.28: Sampler configuration for sampling high-frequency jitter       | 62 |

| Figure 4.29: Correlation of high-frequency DLL jitter                       | 63 |

| Figure 4.30: Input sampler                                                  | 64 |

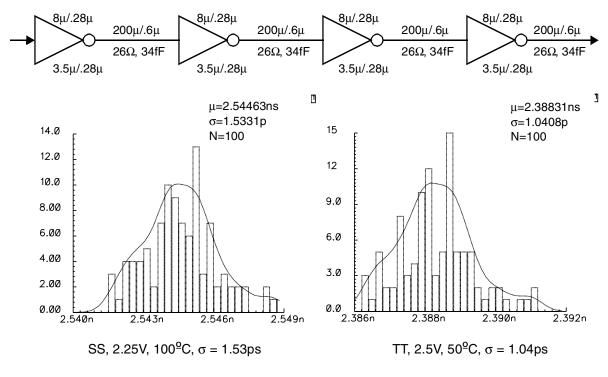

| Figure 4.31: Monte-Carlo analysis of sampler offset voltage                 | 65 |

| Figure 4.32: Input sampler with offset compensation                         | 65 |

| Figure 4.33: Histogram plot of sampler input referred offset voltage        | 66 |

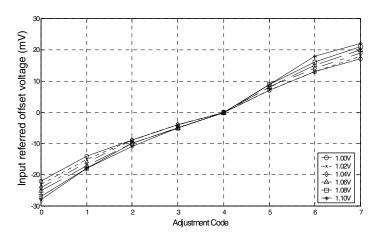

| Figure 4.34: Measured sampler offset adjustment range                       | 66 |

| Figure 4.35: Sampler offset compensation stability versus temperature       | 67 |

| Figure 4.36: Sampler offset compensation stability versus input common-mode | 67 |

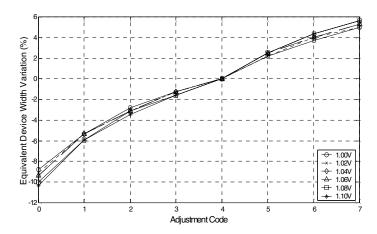

| Figure 4.37: Sampler beta compensation stability versus common-mode         | 68 |

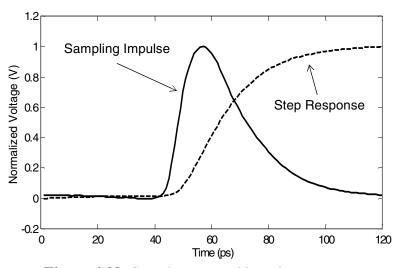

| Figure 4.38: Sampler step and impulse responses                             | 68 |

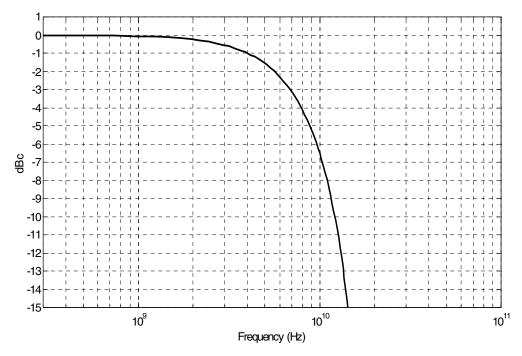

| Figure 4.39: Frequency spectrum of sampling impulse                         | 69 |

| Figure 4.40: Experimental test chip micrograph                              | 70 |

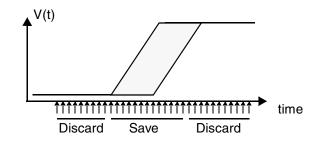

| Figure 5.1: Interconnect between instrumented logic and sampling system     | 75 |

| Figure 5.2: Topology for measuring interconnect delay                       | 76 |

| Figure 5.3: Increasing static delay measurement with induced jitter         | 77 |

| Figure 5.4: Matching for 800µm of interconnect                          | .78 |

|-------------------------------------------------------------------------|-----|

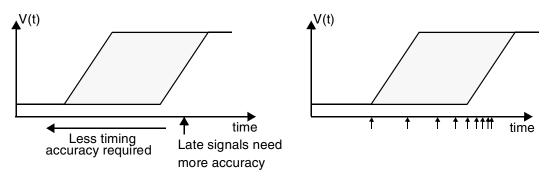

| Figure 5.5: Logarithmically encoded edge information                    | .80 |

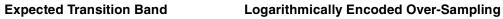

| Figure 5.6: Window based decimation of sampler data                     | .81 |

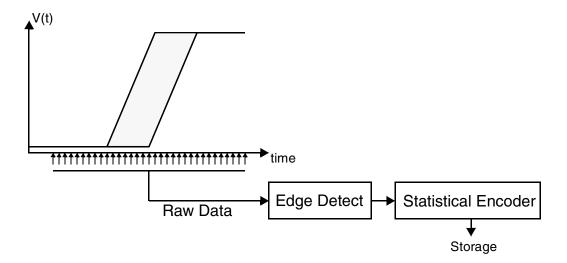

| Figure 5.7: Edge detection and compression                              | .81 |

| Figure 5.8: Real-time jitter compensation                               | .82 |

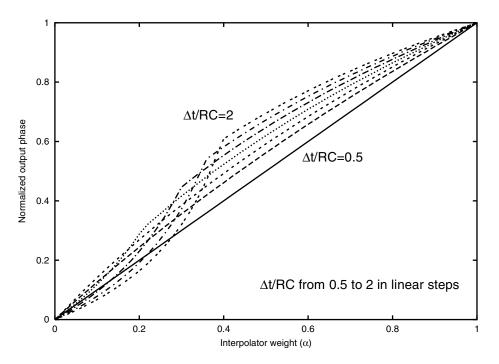

| Figure A.1: Interpolator operation                                      | 89  |

| Figure A.2: Interpolator model                                          | .90 |

| Figure A.3: Linearity of interpolator model with unit step inputs       | .90 |

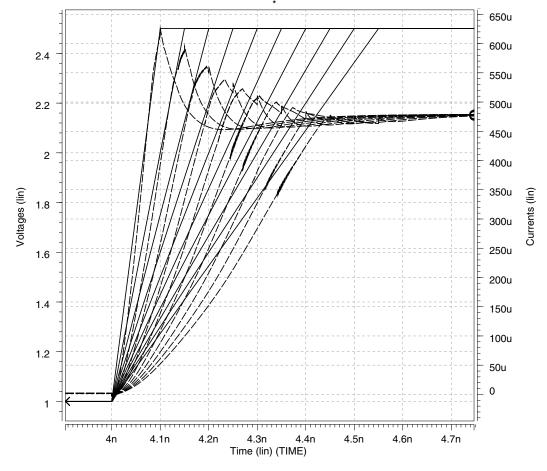

| Figure A.4: Interpolator current versus input rise time                 | .91 |

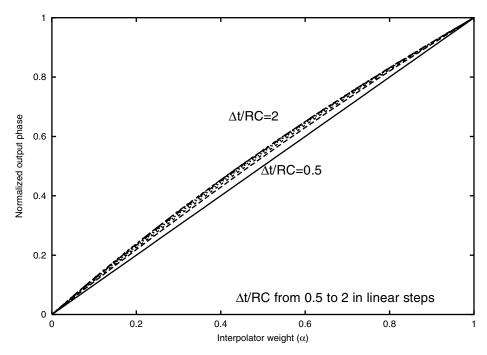

| Figure A.5: Linearity of interpolator model with finite-risetime inputs | .93 |

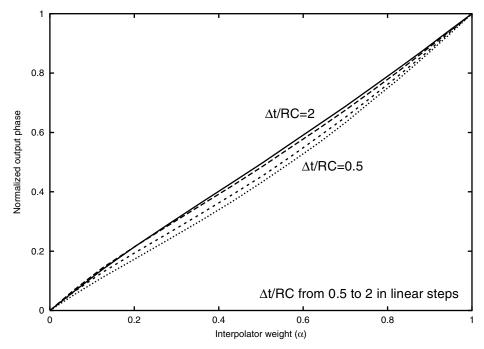

| Figure A.6: Linearity of interpolator SPICE model                       | .93 |

# Introduction

"If I had more time, I would write a shorter story."

#### - Mark Twain

Every CMOS VLSI chip that is produced needs to be tested to ensure it was manufactured correctly. Test and possible debug has always been a challenging task that requires specialized hardware "testers." Furthermore, the rapid scaling of chip performance is making test increasingly difficult. Until recently, testers were able to leverage process technologies with intrinsic performance greater than CMOS to obtain sufficient timing capabilities to accurately test CMOS parts. However, because the performance of CMOS technology has scaled faster than the performance of other process technologies, using non-CMOS process technologies to build testers suitable for testing modern VLSI parts is becoming more difficult.

CMOS process scaling has not only enabled faster clock rates, but also increased chip functionality. As technology scales, more complex designs can be integrated on a chip to improve performance, because on-chip communication is vastly faster than external interconnects. However, an undesirable effect of integration is a reduction in the observability of the system, and, as a result it is more difficult and costly to test and debug a part. Building the tester pin electronics in CMOS and in some cases, even integrating the pin electronics into production parts can address both performance and observability and lead to easier test and debug. This thesis addresses key issues in building high-speed testers in CMOS.

## **1.1 Test Overview**

The purpose of a VLSI tester is to drive a part with known values and to verify that the outputs of the part are correct. In addition to pass/fail production test, testers are also used for debugging and performance characterization. A block diagram of a tester's basic

Figure 1.1: Basic tester architecture

function blocks is shown in Figure 1.1. While this figure only shows a single transmitter and receiver channel, modern testers are typically composed of hundreds, or thousands, of such channels. The *device under test* (DUT) is socketed on a custom printed circuit board (PCB), known as a *load board*, that interfaces the part to the tester. The tester drives the DUT with data vectors that are either algorithmically generated at run time or pregenerated and stored in a memory. The tester samples the DUT outputs and compares them to expected values which are also read from memory or generated on-the-fly. The pin electronics drives input data and samples the DUT with specified timing. Building high-speed pin electronics with precise timing that can scale with the performance of CMOS parts is a significant challenge.

The I/O frequencies of CMOS parts have historically scaled in a very limited manner primarily due to signal integrity issues at the system level [15].<sup>1</sup> This has been beneficial for test because the same tester could be used to test multiple generations of CMOS parts. But eventually higher speed I/O is required because insufficient chip I/O bandwidth limits the part functionality. This problem has been partly addressed by increasing the number of

<sup>1.</sup> As an example, the I/O bus on Intel IA32 processors has increased in frequency by a factor of four (33MHZ to 133Mhz) over a period of roughly a decade (from 1990 to 2000). However, processor performance has increased by roughly a factor of thirty over the same period.

I/O pins with advanced packaging techniques, such as flip-chip bonding, but these solutions are limited by routing considerations in both the chip substrate and the printed circuit board. Further efforts have focused on high-speed I/O techniques, which are becoming an increasingly common method for improving system bandwidth. This is evident in high-end networking chips, which can have I/O frequencies in excess of 3GHz [45], and in more mainstream systems, such as personal computers, that contain a number of parts with high-speed interfaces such as RDRAM [44], DDR-SDRAM [43], and AGP [42] graphics chips.

Testing parts with high-speed I/O is difficult because data must be driven and sampled by the tester at high frequencies and with precise timing. In the past, manufactures of test equipment have been able to leverage the intrinsic performance of expensive process technologies, such as Gallium Arsenide (GaAs) and Silicon bipolar. These technologies, while not supporting the integration densities of CMOS, have had faster devices and thus could be used to build a tester with sufficient performance to test CMOS parts. However, the performance of CMOS technology now matches or exceeds the performance of many GaAs and bipolar technologies, primarily due to the larger research and development efforts directed towards it. The result is that performance of technologies that have historically been faster than CMOS, such as GaAs, can no longer be leveraged to build testers capable of testing the fastest CMOS parts.

The increase in chip and I/O frequencies has not only made traditional testing more difficult but has also created a demand for more advanced test and measurement capabilities. Modern testers obtain minimal timing information because they only test the output of a part at specified times for the correct value. However, knowing when edges transition is more useful when dealing with timing issues. For debugging, edge transition information allows a better understanding of the characteristics and effects of jitter. For production, this information can potentially enable faster characterization of part performance and margins.

An alternative to building parts with high-speed I/O is integrating the parts that must communicate at high speeds onto a single chip (termed a *system-on-a-chip* or *SOC* for short). While this avoids the problems of testing parts with high-speed interfaces, the

communication between components integrated on the SOC can no longer be easily observed because probing on-chip signals is much more difficult than probing printed circuit board traces. This makes test and debug more difficult and expensive. A solution to this problem is to embed part of the tester onto the die so that it can capture the state of the internal signals and restore observability.

## 1.2 Goals

The goal of this thesis is to build a CMOS input receiver with high timing accuracy and edge-detection capabilities that is suitable for both stand-alone and embedded testing applications. This work is focused on receivers rather than transmitters because edge detection requires more sophisticated receivers, but not transmitters, and for embedded applications, a receiver is more useful because it increases circuit observability.

#### 1.2.1 Organization

To better understand tester constraints and technology options, Chapter 2 surveys the evolution of tester technology and existing research work. This includes state-of-the-art testers, experimental CMOS tester architectures and future trends. Challenges and requirements of next-generation testers are described which leads to a promising approach, CMOS oversampled receivers. Oversampled receivers can record detailed timing information and are well suited for implementation in CMOS. CMOS however, has not been historically competitive with GaAs and bipolar for building circuits with precise timing. Therefore, Chapter 3 investigates the timing limitations of a CMOS oversampled receiver. It includes the sources and characteristics of timing errors and compensation techniques which make CMOS timing accuracy competitive with other process technologies. Chapter 4 explores the implementation issues of a CMOS, multi-channel, oversampled receiver and presents experimental results for the compensation techniques presented in Chapter 3. As parts gets larger and more complex, integrating tester receivers onto production part becomes more attractive. Chapter 5 considers the issues involved including required hardware, inter-connect issues, and data processing. Chapter 6 concludes this work.

# Background

"A man with a watch knows what time it is. A man with two watches is never sure."

#### - Segal's Law

The evolution of VLSI parts has required changes in tester design. In the past, the changes have been primarily focused on I/O pin density rather than operating frequency or timing accuracy because the technologies used to build pin electronics, bipolar and GaAs, were well suited for high performance applications, but less capable of supporting high levels of integration. Prior research has explored CMOS alternatives to address the integration issues, but because of the performance gap between CMOS and bipolar or GaAs, pin electronics continue to be built with GaAs or bipolar.

CMOS is a very attractive technology because the performance and integration is scaling at a sustained rate that is faster than any other process technology. The next section examines how the advantages of CMOS relate to testing and the potential benefits of a CMOS tester. This is followed with two sections, 2.2 and 2.3, that expand on integration and performance issues, which are the two primary issues confronting the design of testers. All described in Section 2.3 are some promising circuits that provide sufficient performance for high speed test and prepares the reader for a more detailed examination of the timing issues presented in Chapter 3.

## 2.1 The Allure of CMOS

Tester pin electronics are commonly built in GaAs and bipolar technologies because they have historically had a performance advantage over CMOS, but the rapid scaling of CMOS technology makes it an attractive alternative, as evident in Figure 2.1. Because of

Figure 2.1: Comparison of  $f_T$  for GaAs, Bipolar and CMOS devices (Courtesy of C.-K. K. Yang)

the rapid scaling of CMOS, extrapolating the data in Figure 2.1 indicates that in the near future, the performance of CMOS devices will exceed that of GaAs and bipolar devices.

While the performance of CMOS devices is just becoming comparable with GaAs and bipolar devices, CMOS does have the distinct advantage of superior process integration. This enables the construction of highly integrated testers that can support the large numbers of pins required by modern parts. Using technologies with less integration capabilities than CMOS results in physically large and bulky machines, such as shown in Figure 2.2.<sup>1</sup> Furthermore, GaAs and bipolar solutions typically consume more power than equivalent CMOS solutions<sup>2</sup> and testers built with these technologies can require 100 or more watts per pin [41]. Extracting the resultant heat can further limit the density of the

<sup>1.</sup> To be fair, the pin electronics do not fill the entire tester shown in Figure 2.2. The rectangular box contains power converters, auxiliary test instrumentation (such as pulse generators or time interval analyzers), and sometimes a workstation for control. The circular unit, called the *test head*, contains digital parts for vector storage and generation, in addition to pin electronics and timing circuitry, which drive and sample the DUT with precise timing.

<sup>2.</sup> Finding similar CMOS and bipolar parts to enable a comparison of power is difficult. However, bipolar is generally regarded as higher power and as an example, a sixteen channel CMOS tester part [12] discussed later in this chapter consumes less than 1W, while a three channel bipolar part built by AMCC for MegaTest consumes over 5W [3].

Figure 2.2: A modern VLSI tester (Teradyne J973)

electronics. Because of these integration constraints, bipolar and GaAs pin electronics are usually not highly integrated and one or more parts are required per pin. However, given the integration potential of CMOS, significantly more integrated testers are feasible. A decade old CMOS part presented in the next section integrates sixteen I/O channels and it is reasonable to envision even higher integration using more modern CMOS processes.

In a sense, modern chip testers are analogous to mainframe computers. They are both hand assembled to custom specifications provided by the customer, they eschew highintegration for the sake of performance and the result is similar: large, expensive machines that cost millions of dollars. In years past, the cost of a mainframe was justified by using it to serve many users via remote terminals. Modern testers are similar: to lower the amortized cost of testing, many parts are tested in parallel on a single tester.

The problem with the mainframe model is that despite being amortized across many desktops, they are still expensive. Furthermore, the complexity of the machines makes the design cycles long. For processors, new and simpler solutions that better leverage the advantages of CMOS have significantly closed the performance gap. The result is that mainframes are now confined to a niche market, while personal computers proliferate. If testers were to follow a similar path, the result would be smaller, less expensive and higher-performance machines.

Figure 2.3: Pin count trends

# 2.2 I/O Channel Requirements

The cost and size of a tester is greatly influenced by the number of I/O channels it contains. Unfortunately, as CMOS VLSI parts increase in performance and functionality so do the I/O requirements. This is quantified by the empirical formula known as Rent's rule:

$$Np = Kp \cdot Ng^{\beta},$$

where Np is the number of external connections, Ng is the number of gates on the chip, and Kp and  $\beta$  are empirically determined constants. When originally formulated, this equation assumed that the I/O speed was the same as that of the internal clock, however, in modern parts this is not the case. Nevertheless, the observation that an increase in I/O is required as parts become larger and more complex, is still valid and historical data indicates that the number of I/O pins on a chip has scaled by about 12% per year as shown in Figure 2.3 [8]. Contemporary testers can have thousands of pins and must continue to scale with the pin counts of VLSI parts. Physically large pin electronics are required to support large numbers of I/O channels because of limited integration. Connecting the pin electronics to the DUT then requires long cables or PCB traces. If the wavelength of the highest frequency of interest is comparable to the length of the signal path, then the connection cannot be viewed as a lumped model and the transmission line characteristics, such as reflections, must be taken into account. Reflections will distort the waveform unless the line is properly terminated, but this is only possible if the driver is capable of driving the termination impedance. While most tester pin electronics and high-speed I/O drivers are capable of driving terminated transmission lines, this is not a general characteristic of all CMOS parts. Furthermore, frequency dependant attenuation in the transmission line can still reduce timing accuracy even in a properly terminated transmission line<sup>1</sup>. The result is that small, integrated pin electronics are desirable to maintain short signal paths between the tester and DUT.

To achieve better integration and lower costs, two CMOS architectures, the Data Generator Receiver (DGR) and Testarossa, were developed at Stanford University in the late 1980's. Increased integration permits the placement of multiple I/O channels and additional tester circuitry onto a single die. This enables the construction of testers with large numbers of I/O channels while at the same time, maintaining short signal paths between the tester and DUT.

The DGR integrated sixteen I/O channels and a 256 cycle vector memory onto a single chip [23]. It was intended only for functional test and therefore could only to drive and sample the DUT on clock cycle boundaries. Nevertheless, this part demonstrated the feasibility of building a complete single-chip, CMOS functional tester.

The Testarossa improved on the DGR by adding pin electronics and timing capabilities [12]. Pin electronics enable the tester to drive more complex waveforms than the DGR for richer test capabilities. The timing features allow the tester to generate output and sampling signals that transition at arbitrary locations within the clock cycle. Tunable

<sup>1.</sup> Dielectric loss and skin effect are the dominant loss mechanisms in printed circuit boards and cables, respectively. Attenuation of the high-frequency components can cause intersymbol interference which is a form of a data dependant timing error.

timing verniers constructed from static CMOS gates permitted fine edge placement. Precise timing accuracy was achieved by using a high-precision external delay generator.

Because timing issues such as skew and jitter were not significant issues at the time the Testarossa was built (1989), little attention was focused on these issues when designing the circuits. So while the Testerossa demonstrated the potential of CMOS testers, it lacked sufficient timing performance to test modern parts and unfortunately, these timing issues are only becoming worse.

## 2.3 Timing Performance

Ideally, a tester drives data to the DUT and samples the outputs at exact moments in time as specified by the test program. However, timing uncertainty limits the accuracy of when an edge is driven or when an output is sampled. This timing uncertainty is due to both the tester pin electronics and the connection between the tester and DUT.

To compensate for this uncertainty, testers are run conservatively with a timing margin that is sufficiently large to ensure a part that cannot meet timing requirements will not be incorrectly marked as functional. This timing margin is termed the *guard band* and is equal in magnitude to the timing error of the tester. The larger the tester guard band, the more conservative the test margin. Conservative testing implies that marginal parts are discarded despite meeting specified timing requirements. As I/O rates increase, the size of the required guard band is an important parameter and timing uncertainty becomes a critical performance metric for VLSI testers.

Unfortunately, the timing accuracy of testers is not scaling with the cycle time which is a problem because they are consuming an increasing large percentage of the cycle. A tester for 100MHz SDRAM has a cycle time of 10ns and a timing uncertainty +/-125ps [46]which is 2.5% of the cycle, but a modern RDRAM tester has +/- 50ps uncertainty, which is 8% of a 800MHz cycle [41]. The implies that parts with high-speed I/O either have a lower yield or are binned into slower frequency ranges because of tester limitations.

Testing methodologies can increase the impact of guard bands because it is not uncommon for parts to be tested by multiple parties while transitioning from

Figure 2.4: A time digitizer

manufacturing to final product integration. If each party tests the parts with the same guard band, then it is possible for the part to pass an initial test but fail a subsequent test. It is important that the supplier provides the integrators with parts that meet or exceed the published timing specification. Testing a part with a double guard band ensures that it will always pass tests that use a single guard band. However, a double guard band provides no margin for error and so at times, manufactures test with an even more conservative triple guard band.

#### 2.3.1 Detailed Timing Information

One way to reduce some of the overhead due to guard bands is to capture edge timing information. Traditional testers verify DUT outputs by sampling at preset positions within the cycle to determine if the outputs are correct. But knowing when edges transition enables a test program to interpret the magnitude of a timing failure rather than treating all errors as identical.

Edge timing information also provides cycle to cycle jitter and timing margin measurements which are very useful when characterizing high-speed designs. Zargari recognized the need for increased timing information during testing and the result was a BiCMOS time digitizer that incorporates edge detection capabilities for 2 input channels [37]. A simplified block diagram for the time digitizer architecture is shown in Figure 2.4. The input signal clocks a register that captures the state of a high-speed counter to record the time of the input transition. The resolution of the part is 90ps with an accuracy of 38ps

Figure 2.5: An oversampled receiver

in a 0.6um BiCMOS process. High levels of integration are possible by sharing the multiphase clock generator among multiple input channels.

An interesting characteristic of the time digitizer is that it only outputs a digital value when the input edge transitions. Thus, the output data rate is set by the number of transitions of the input. For some applications where timing information is desired for relatively infrequent events, such as physics experiments, this results in a form of output data compression. However, in a tester application, sampling on transitions is less of an advantage because the inputs can transition at higher rates which result in a large output data bandwidth. Furthermore, the output data rate is dependent on the input transition rate. A series of closely spaced input edges can cause the output data from one edge to overwrite the data from a previous edge.

The main limitations of this approach are due to the data signal being used as a clock. The input samplers require a clock of finite width, so narrow data glitches cannot be captured. Low-swing input signals are also a problem because they are less effective as clocks compared to full-swing signals. This is a significant problem because low-swing signals are common in high-speed I/O. The clock can be amplified to full-swing, but the amplifier will add timing uncertainty to the system.

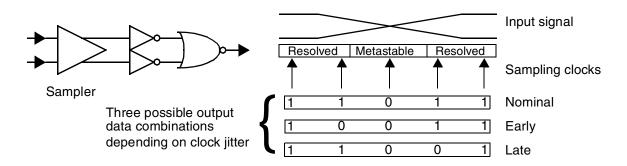

#### 2.3.2 Oversampling Receiver

Switching the role of the clock and data results in an oversampled receiver that eliminates the drawbacks associated with the time digitizer. A block diagram of an oversampled receiver is shown in Figure 2.5. By sampling the data signal at a very high

Figure 2.6: Fanout-of-4 inverter delay

rate, as compared to the input frequency, input transitions are captured with precise timing. If a cycle is defined as 1/f where f is the maximum input frequency, then the number of samples in a cycle is termed the *oversampling rate* (or for brevity, just the *sampling rate*).

The sampling rate limits the achievable timing resolution and is itself limited by CMOS transistor performance. A good metric for quantifying CMOS performance is the delay of a fanout-of-4 inverter (*FO-4 delay*) as shown in Figure 2.6 While the delay of a FO-4 inverter is process dependant, the ratio of a FO-4 delay to the delay of other more complex gates is relatively independent of process [34]. Therefore, a FO-4 delay metric provides a relatively accurate indicator of digital circuit performance independent of process technology. From simulation, the minimum pulse width that can be propagated through a chain of CMOS inverters without attenuation is about three FO-4 delays, which results in a clock period of twice this, or six FO-4 delays. This includes little margin, so eight FO-4 delays is a more realistic limit. Either yields a sampling resolution too low for a modern tester application. Fortunately, it is possible to use more transistors to compensate for device performance by time-interleaving multiple samplers as shown in

Figure 2.7: A CMOS implementation of an oversampling receiver

Figure 2.7. The set of time-interleaved flip-flops that samples the input is termed an *input channel*. Multiple input channels can share a single clock generator to permit highly integrated testers. This type of CMOS receiver has found previous application in high-speed communication systems [36].

In an oversampled architecture, the sampling flip-flops can be clocked sense amplifiers which allows the receiver to capture both low-swing and glitching input edge transitions. The samplers generate a constant stream of data representing the state of the input signal. While an oversampled receiver does not compress the output data as with a time digitizer, it does has the advantage of generating data that is synchronous with sampling clock. This can simplify the circuits required for acquisition and processing of the data. The sampling frequency is set by the design of the oversampled receiver and is independent of input signal transitions.

While an oversampled receiver can be used to capture input transition information and serve as the basis for a tester input receiver, the timing accuracy limitations are not clear. Chapter 3 explores how static phase offsets, jitter and input bandwidth restrictions limit timing accuracy.

# **Timing Accuracy**

"In theory, there is no difference between theory and practice; In practice, there is"

#### - Chuck Reid

High-speed interfaces require testers with high timing accuracy. However, timing accuracy in an oversampled receiver is limited by numerous error sources. To understand the applicability of this technology to chip testing and to categorize the potential performance, this chapter identifies and characterizes these error sources. Once this has been done, compensation techniques are considered to yield an understanding of the fundamental timing limitations.

This chapter starts by examining multi-phase clock generators since they are a significant source of timing errors in an oversampled receiver. Sections 3.2 through 3.4 cover error sources within clock generators that limit timing resolution. Also presented are measurement and calibration techniques to maximize timing performance in the presence of error sources. The chapter ends with a discussion of the timing errors introduced by the clocked sampling receivers.

#### 3.1 Multi-Phase Clock Generation

The discrete sampling nature of an oversampled receiver fundamentally limits the achievable timing accuracy to  $\pm \tau/2$  for a sample spacing of  $\tau$ . Increasing the sampling resolution requires high-frequency or finely spaced sampling clocks. The maximum frequency of a clock generator is fundamentally limited by the ability to propagate clock pulses through CMOS inverters which are the most basic form of a clock buffer. As mentioned in Chapter 2, the minimum pulse width that can be propagated reliably without attenuation is about four FO-4 delays which results in a clock period of twice this, or eight FO-4 delays. This sets an absolute limit on the sampler clock frequency.<sup>1</sup>

Figure 3.1: Multi-phase clock generators

To achieve faster sample rates, multiple interleaved samplers can be clocked with evenly phase shifted clocks. Two common CMOS implementations of multi-phase clock generators are shown in Figure 3.1. The control loop (phase detector, charge pump and loop filter) servos the control voltage of the delay elements, so that the propagation time of an edge through the delay elements is locked to the reference period. In a delay locked

<sup>1.</sup> An oversampled system requires a high clock rate to maintain high timing precision, but this can be an issue when testing synchronous parts. During frequency binning, the frequency of a part is swept to determine the maximum operating speed. Usually, the frequency of the tester is also swept as well, but if the operating frequency of the oversampled receiver is reduced to match the part, the timing accuracy of the receiver degrades. While the reduction in timing accuracy scales with cycle time, it still has the effect of increasing the guard bands as the frequency is reduced. However, the output of an oversampled receiver is just edge transition timing information with no inherent concept of cycles, and therefore the tester receiver can be run at maximum frequency independent of the part frequency to avoid this issue.

loop (DLL), the delay elements delay the incoming clock, while in a PLL, the delay elements are connected in a ring to form a voltage controlled oscillator (VCO). By matching the buffer elements that compose the delay line or VCO, multiple, uniformly spaced clock phases are created. In Figure 3.1, the delay line is locked to only half the period of the reference clock because differential buffers can generate the complementary outputs. For single-ended delay elements, the number of delay elements in the delay line can be doubled and locked to 360° rather than 180°. The matching buffers at the beginning of the DLL pre-condition the input edge rate and signal swing so the first delay line buffer has an identical input edge as the last buffer element. Those at the end equally load the last buffer cell to reduce phase offsets.

In both the PLL and DLL, the spacing of the clock phases is limited to the minimum propagation time through a delay element. If the loads on the DLL or PLL are much smaller than the delay cells themselves, the minimum phase spacing can asymptotically approach a FO-1 delay. While one might expect a FO-1 delay to be a quarter of a FO-4 delay, it is actually not quite that small. This is due to the additional self-loading of the inverter diffusion capacitance. This capacitance is typically a factor of one-half to one of the input gate capacitance. Therefore, a FO-1 delay is only 2-3 times smaller than a FO-4 delay, which, in a  $0.25\mu$ m process, results in a FO-1 delay of roughly 50ps. Not only is this larger than the resolution required to test a modern part, but it does not include a mechanism to control the delay of the buffers. Delay tuning transistors or capacitors will almost certainly increase the minimum delay. Finally, even if a FO-1 delay were sufficient, there is no provision to increase the resolution (other than changing processes) should it be required to do so in the future. So while this would enable a tester to scale with process technology, it does not allow scaling at a rate faster than process technology. What is needed is a technique to generate phase spacings that are a fraction of a gate delay.

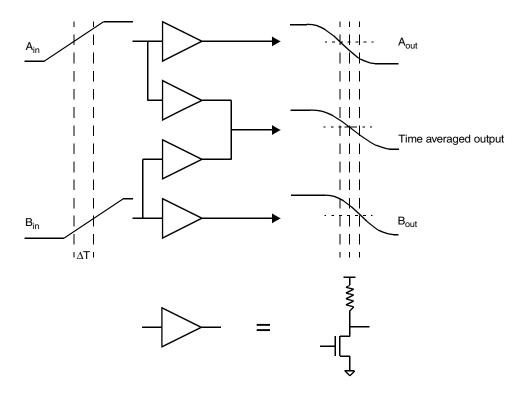

Phase interpolation is an established technique for generating edges with finer timing resolution compared to what can be achieved with individual buffers. This is accomplished by blending two phase-shifted edges to produce a new edge that transitions in between the existing edges. An interpolating element composed of two inverters is shown in Figure 3.2. On the right side of the figure are three output waveforms. The top

Figure 3.2: Interpolator operation

and bottom waveforms are the result of passing the two inputs through normal inverters. The middle output waveform is created by shorting the outputs of two inverters together. The result is a "smeared" output curve formed by the merged drivers.

Finely space clock edges can be generated by interpolating between coarsely spaced clock edges created with a traditional clock generator, such a PLL or DLL. In theory, interpolation can be recursively applied to create arbitrarily small phase spacings. However, in practice, the achievable phase spacing is limited by numerous error sources that are discussed in the following sections.

## **3.2 Timing Accuracy**

Static and dynamic variations in the position of clock edges from their ideal locations is a significant obstacle to building high-precision clock generators. Static variations, termed *static phase offsets*, are clock edge placement errors caused by fixed error sources such as device variations, circuit mismatches and layout asymmetries. Dynamic variations, termed *jitter*, can be grouped into two categories: deterministic and random [21]. Random jitter (RJ) is caused by fundamental noise sources in the clock generator such flicker and thermal noise. Deterministic jitter (DJ) is caused by variations in the clock edge due to deterministic and bounded sources, such as power supply noise.

Figure 3.3: Sample DNL and INL for a six-phase clock generator

Deterministic error sources dominate on large digital chips, such as microprocessors, that are the target environment of this work. For this reason, RJ is not considered further.<sup>1</sup>

## 3.3 Static Phase Offsets

Generating precisely aligned clocks requires precise matching between the circuits that produce and buffer each phase. However, device mismatch and physical limitations in layout reduce this symmetry and therefore disturb the ideal phase alignment and produce timing offsets. As the spacing between clock phases is reduced and becomes a small fraction of a gate delay, static offset errors becomes a more significant fraction of the timing resolution.

Clock phase spacing errors can be characterized by differential non-linearity (DNL) and integral non-linearity (INL) as shown in Figure 3.3. For a tester, one might assume that INL limits timing accuracy because it is the difference in timing between actual and ideal clocks. But if the timing of clock edges can be measured, then the timing difference between the actual and ideal clocks will not reduce accuracy. What cannot be corrected

<sup>1.</sup> Periodic steady state (PSS) analysis using the Cadence Spectre RF simulation indicates 3σ RJ for a CMOS PLL implementation to be around 1.3-1.8ps. Measured jitter including both RJ and DJ is normally at least an order or magnitude larger.

though, are DNL errors which are due to non-uniform spacing of the sampling clocks. In the context of an oversampled receiver, the time between two clocks is termed a *sampling bin*, and in places within this dissertation, abbreviated simply as *bin*.

It is interesting to note that DNL errors that result in smaller than expected bin sizes will not introduce timing errors by themselves. In fact, timing accuracy is increased over the part of the period where the edges are compressed, since the input edge position can be determined with greater precision. However, a PLL or DLL control loop will drive the sum of the DNL errors to zero and therefore, negative DNL errors implies the existence of positive DNL errors which do reduce timing accuracy by increasing the size of the corresponding sampling bin.

#### 3.3.1 Sources of Static Phase Offset

A significant source of timing errors is device mismatch and asymmetries in circuits and layout. These errors are not fundamental limitations, since device mismatch can be reduced with larger devices and layout asymmetries can be reduced with multiple fabrication trials, but they do present practical limitations. In all real designs, both transistor sizes and design time are limited.

In both a DLL and a PLL, the control loop feedback clock increases the load on one of the output phases. To maintain symmetry, dummy loads are used to balance loading on all phases, but this requires additional area and power. DLLs have further circuit asymmetries because of delay elements required at the ends to the delay line. The buffers at the end of the DLL only cost area and power, but those at the beginning will contribute additional jitter, as described in Section 3.4, because the reference clock edge must traverse through these buffers *before* going through the delay line. Care must be taken to ensure changes made to improve matching do not create additional jitter.

The layout of multi-phase clock generators, especially those with large numbers of clocks is difficult because of matching and the resulting asymmetries are a significant source of static phase offsets. First-order matching of layout capacitance is straightforward, but matching second-order effects, such as coupling between active signals is more challenging. Extraction tools can produce detailed models of the parasitic

Figure 3.4: Multiple clock phases and their noise sensitivity functions

capacitances, but the effect of coupling capacitances depends on the edge rate of the coupling signals, which can change over process corners.

Static phase offsets are also caused by synchronous supply noise at the same frequency as the clock generator. To understand why this happens, consider Figure 3.4 depicting three clock waveforms and the absolute value of their noise sensitivity functions (NSF) as described by Hajimiri and Lee [14]. The NSF of a circuit represents the delay sensitivity of the circuit (in this case, a clock buffer) to power supply noise as a function of time. The value of the NSF is zero when the buffer output is not in transition and non-zero when the output transitions. Noise will only affect the buffer delay when the NSF of that buffer is non-zero.

A synchronous noise source at the same frequency as the clocks is also shown in Figure 3.4. The only buffers affected by the synchronous noise are those with a non-zero NSF at the time the noise event is occurring. Since, by definition, the synchronous noise source is identical every cycle, the affected buffers are influenced every cycle in an equal

manner and hence are consistently fast or slow depending on the nature of the noise source. This assumes that the phase relationship between the synchronous noise and the clocks is constant. If the alignment of the noise and the clock varies slowly (perhaps due to temperature variations perhaps) then static offsets due to synchronous noise that are measured and calibrated at start-up can re-manifest themselves as the temperature and supply voltage of the part changes over time. If synchronous noise constitutes a large fraction of the static phase offsets, calibration is more difficult since it must be run often enough to the track changes in the noise characteristics. Fortunately, the effect of these error sources need not be large and, at least for the design presented in Chapter 5, they are not a significant issue.

#### 3.3.2 Measurement and Calibration

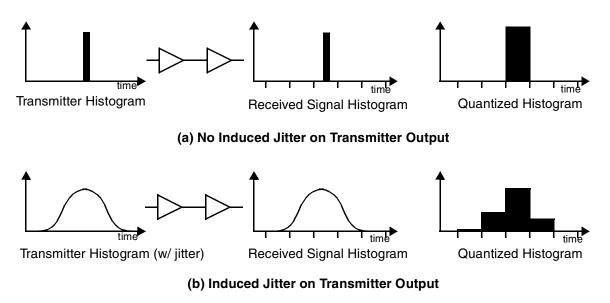

Static phase errors are a significant source of timing errors, but can be reduced with calibration. The position of the clock edges can be measured with averaged phase timing measurements using histogram counters [18]. Given the static position of the clock phases, static phase errors are removed by tuning adjustable interpolators within the clock generators. The timing accuracy after calibration is limited by the resolution of the interpolators. Published results have demonstrated interpolators that can be adjusted over a range of a FO-4 delay with 4 bits of resolution and a DNL of less than one LSB (1/16 of a FO-4) [30].

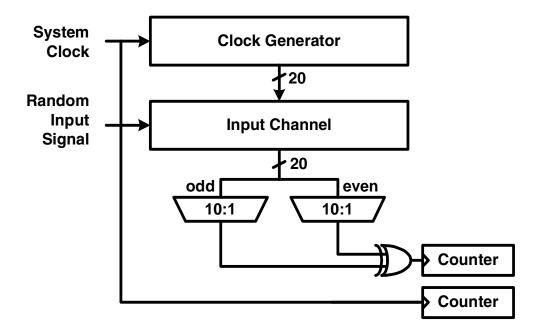

Averaged phase timing measurements do not limit the achievable timing accuracy provided they are performed over sufficiently long periods so that dynamic errors due to jitter average to zero. The measurement is performed by sampling a random signal with the multiple clock phases, as shown in Figure 3.5. Histogram counters record the number of input transitions between adjacent samplers. An additional counter limits the acquisition period by counting system cycles. If the input signal edges are randomly distributed within the cycle and the sampling clock edges are evenly spaced, then the histogram counters will have identical values. If the sampling clocks are unevenly spaced due to static phase errors, the counters will not be equal and the difference will be proportional to the phase spacing error.

Figure 3.5: Histogram measurement of static clock phase alignment

Input transitions are detected within sampling bins when the XOR of two adjacent sampler outputs is a logical one. While a random input signal is sufficient, it is useful to consider the desired characteristics of the input signal with more detail. The frequency of the input signal must be constrained so that it evenly cycles through the sampling bins. For instance, if the input signal is the same frequency as the clock generator, the input transitions will not cycle through all the bins and an accurate histogram cannot be measured. If the input signal has a period that is two-thirds of the clock generator, then the input edge placement will repeat every 3 cycles. To ensure that quantization noise in the measurement does not limit calibration, the input signal must be constrained such that,

$$\frac{LeastCommonMultiple(F_{sys}, F_{inp})}{F_{sys}} > BinCount \cdot \left(\frac{T_{bin}}{T_{adj}}\right).$$

$F_{sys}$  is frequency of the clock generator  $F_{inp}$  is the frequency of the input signal  $T_{bin}$  is the resolution of a bin  $T_{adi}$  is the resolution of a LSB This implication of this equation is that there must be enough unique input edges within a cycle so that the measurement resolution is at least as large as the resolution of the interpolation adjustment. Otherwise, the interpolator would be able to move an edge with greater resolution than could be measured. Sampling clock jitter does not affect this measurement because it is just as likely to make a sampling bin smaller than larger and thus averages out for a sufficiently large histogram period. Sampler input offsets will skew the histogram measurements and need to be minimized before this measurement technique is used.

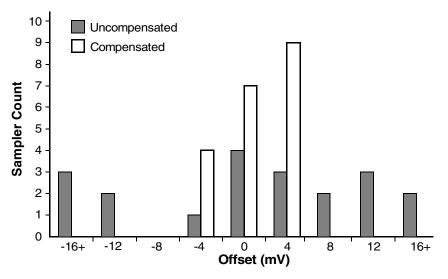

Given the ability to position to a clock edge within 1/16 of a FO-4 delay [31] and measure the timing of clock edges to an arbitrary precision [17], it appears possible to constrain phase errors to within about 3% of a FO-4 delay. This is significantly better than previously reported data for multi-phase clock generators. Maneatis in [23] reports DNL phase spacing errors of 14.3% of a FO-4 delay in a 2µm process and Yang reports similar DNL measurements in [37] for uncompensated clock generators. Potentially even more important however, is the robustness of the technique as unexpectedly large static phase offsets are a reoccurring theme found in many papers that report DNL measurement for multi-phase clock generators [6][23][37]. Even the test chip presented in Chapter 5 had larger than expected phase errors due to matching issues within the DLL that went unnoticed during the initial design. With sufficient adjustment range, even large unexpected errors can be compensated rather than requiring a redesign, new masks and the associated manufacturing delay. Given that static phase offsets can be controlled, system performance will then be limited by jitter which is described next.

# **3.4 Deterministic Jitter**

Deterministic jitter is caused by variations in the propagation time of delay elements and clock buffers. It is caused by noise modulating the delay of clock buffers and delay elements and limits the timing accuracy of an oversampled receiver by introducing timing uncertainty in the acquired data. The delay sensitivity of a circuit to supply noise can be quantified as:

Power Supply Delay Sensitivity =  $\frac{\% \text{ change in delay}}{\% \text{ change in power supply}}$ .

Figure 3.6: DLL and PLL jitter accumulation

Jitter can be reduced by decreasing the supply sensitivity of the clock generator. This has been the focus of much research and the result is delay elements with a supply sensitivity that is more than an order of magnitude better than a CMOS inverter [25]. Unfortunately, clock buffers are still generally built with CMOS inverters. Jitter introduced by the clock buffers is a significant limitation to achieving low-jitter sampling clocks in a multi-channel oversampled receiver because long clock chains are required to drive the large clock loads.

Power supply noise is typically the dominant source of jitter in CMOS parts primarily because the circuit styles and architectures currently employed have large transient current variations. CMOS logic draws little or no power when idle, but large currents when switching. Furthermore, the common practice of aggressive clock gating in modern parts to conserve power can cause significant current spikes. Current transients combine with the inductance and resistance of the power supply network to produce voltage fluctuations that ripple through the supply network. This problem is becoming more severe with each generation of VLSI parts as the supply voltage is trending downward, but the dissipated power is remaining relatively constant. Therefore, the required supply current and associated dI/dt spikes are increasing.

As a clock edge propagates through multiple delay elements, the jitter introduced by those elements is additive and results in an accumulation of jitter. DLL based clock generators typically have less jitter than a PLL based design because jitter accumulation is limited to the longest path through the delay line and clock buffers, as shown in Figure 3.6. A PLL however, recirculates clocks phases in the VCO and in the absence of a control

loop, jitter accumulation is unbounded. Given a control loop, the jitter accumulation in the VCO is bounded, but even under optimistic conditions, it is still about six times the peak of a delay line [32]. In practice however, such a major discrepancy in jitter performance does not exist because, as described in the previous section, the noise sensitivity of the delay elements is much better than that of the clock buffers.

Jitter can be quantified as either absolute or cycle-to-cycle. Absolute jitter is the difference between an ideal clock edge and the actual edge, while cycle-to-cycle jitter is the difference between clock periods. In some applications, such as microprocessors, absolute jitter is unimportant because there is no other internal timing reference. For such applications though, cycle-to-cycle jitter is important because it requires adding timing margin to logic circuits to ensure that the results is properly clocked into the following latches or flip-flops. For chip testers absolute jitter is important since the part being tested may contain a PLL or other type of VCO structure that does not track absolute jitter in the tester. The only time base that the two systems have in common is real time and therefore, absolute jitter cannot be ignored.

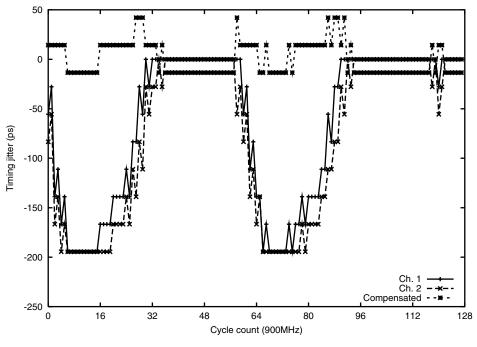

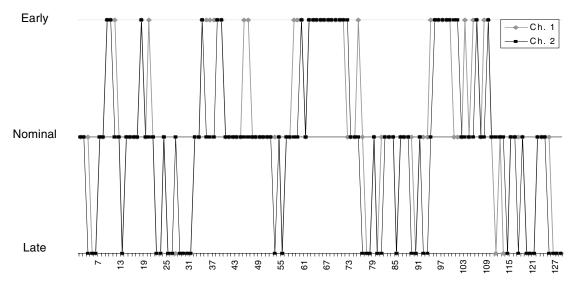

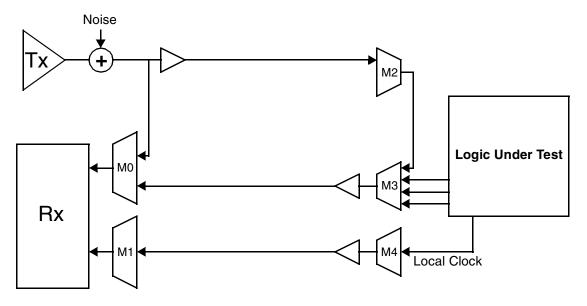

#### 3.4.1 Measurement and Compensation

Both cycle-to-cycle and absolute jitter can be measured by sampling an externally generated reference clock with an input channel. If the reference has low-jitter relative to the sampling system clock generator, any jitter in the measured position of the reference clock can be attributed to the sampling system.<sup>1</sup> If this jitter is correlated between channels, then the jitter measurement from one channel can be used to compensate sampled data from the other channels. While the achievable degree of correlation between channels is not clear, it is reasonable to assume that if the principal source of jitter is the clock generator and drivers, a design that has a minimum of local clock buffering in each channel might have a high degree of correlation in jitter between channels. Data supporting this assumption is presented in the next chapter.

<sup>1.</sup> External crystal and hybrid SAW oscillators with only a few picoseconds rms jitter are available from Vectron International and other suppliers.

Figure 3.7: Ideal input sampler

The bandwidth of the jitter can limit the effectiveness of the compensation. Because the jitter is sampled once a cycle (or twice if both edges of the reference clock are measured), we know by Nyquist's theorem that the maximum frequency that can be measured is one-half the reference clock frequency. Jitter at higher frequencies is aliased down to lower frequencies by the sampling operation and appears as noise in the jitter measurement. The size of the error is determined by the frequency of the reference clock and the power spectrum of the jitter. Fortunately, this does not need to be a significant source of error because high-frequency (multi-GHz) reference clocks can be used in conjunction with the liberal application of on-chip bypass capacitance which limits high frequency noise.

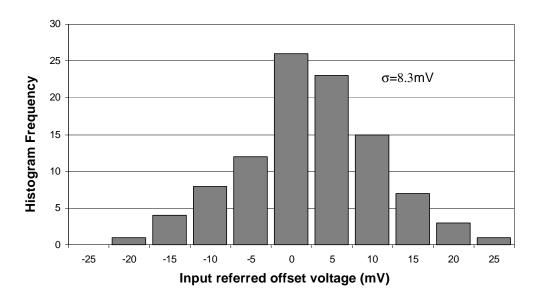

## 3.5 Input Samplers

Having described a technique for generating and measuring the multi-phase clocks, this section explores the issues with input sampler design. A model for an ideal input sampler is shown in Figure 3.7. The input switches are toggled every cycle to instantaneously capture the state of the input signal. The amplifier permits the digital latch to resolve arbitrarily small differences in the sampled inputs. Unfortunately, physically realizable samplers have many non-idealities, not modeled in Figure 3.7, which introduce timing errors.

Device mismatch in both the input switches and amplifier is significant sampler limitation in an oversampled receiver. Mismatch results is a non-zero differential amplifier output for a zero volt differential input. The input voltage that causes a zero differential output voltage is termed the *input referred offset voltage* and can be modeled as a random, but static, error source added to the input signal.

27

Figure 3.8: Differential input receiver with non-idealities

The amplifier has a limited gain-bandwidth product and for small input signals, the amplifier may lack the required gain to overwrite the data latch or storage elements that follow. This introduces hysteresis into the system. However, gain can be increased at the expense of an additional pipeline delay. For this reason, hysteresis in the data latch is not a limiting factor. A model of the input sampler with these effects is shown in Figure 3.8.

A further limitation is the finite bandwidth of the sampling operation. Thus, rather than instantaneously sampling the input signal, the sampler takes a weighted average of the input signal over a finite window in time. The shape of the window depends on both the edge rate of the clocks and type of circuit used. The weighting function is termed the *sampling impulse* or *aperture function* and represents the period over which the sampler is sensitive to the input signal. The minimum width of this curve that includes 50% of the area is termed the *sampling aperture*. The sampling aperture is a useful metric because it specifies the minimum input pulse width that can be captured by the sampler. While described in the time domain, the aperture can also be modeled in the frequency domain as a low-pass filter preceding ideal input switches. All sampling amplifiers have a finite aperture even if they do not have explicit sampling switches. In addition to the input filter due to the sampling impulse, an additional filter exists, formed by the input source resistance and the capacitive load of the sampler inputs. The signal must flow through this low-pass RC filter before it appears at the input of the samplers. Hence, the effective filter is a cascade of the two.

The sampler input filter distorts the shape of the DUT output waveform and can create a static timing error. Prior to test, the delay between the tester and the DUT (due to the test socket, load board and tester cables) is measured so that it can be subtracted from the actual test measurements. Because of the filtering due to the input samplers, the magnitude of the delay depends on the threshold voltage of the input receiver. Testing a part at a threshold voltage different from the threshold used for calibration results in a static timing error.<sup>1</sup> Higher input bandwidths filter the signal less and result in lower timing errors. The interconnect between the DUT and tester will also filter the input so extending the input bandwidth of the sampler significantly past the bandwidth of the interconnect yields diminishing returns.<sup>2</sup>

The input filter is dominated by the input capacitance of the samplers rather than the aperture. An aperture of about 1/4 of a FO-4 delay can be achieved in a modern VLSI processes and results in a very high -3dB frequency [37]. The input capacitance can be quite significant a large number of samplers are connected to the input in an interleaved oversampled receiver. The timing error due to input filtering can only be reduced by increasing the -3dB frequency of the filter. Unfortunately, the source impedance is usually fixed at 50 $\Omega$ , or thereabouts,<sup>3</sup> and thus the only way to increase the -3dB frequency is to reduce the capacitive loading. In some cases, such as the experimental test chip described in Chapter 4, the input capacitance is dominated by ESD protection devices. However, the inputs of embedded testers only sample signals within the die and do not need ESD protection. Therefore, reducing the input capacitance of the samplers and associated wire loading is vital to maintain high timing accuracy.

Reducing the capacitive loading of a sampler requires small input devices. Unfortunately, transistor mismatch is inversely proportional to the square root of the device area. As the devices are made smaller to reduce capacitive loading, the input offset voltage of the sampler increases. The input offset results in a timing error dependant on the input signal slew rate, as shown in Figure 3.9. For signals with a high-slew rate, the effective error due to a given offset voltage is less than for a signal with a slower slew rate.

<sup>1.</sup> Sweeping the input receiver threshold voltage allows the creation of a shmoo plot of the input signal.

<sup>2.</sup> For this reason, and to minimize TDR errors, it is beneficial to build a tester load board with high-quality printed circuit board material with low dielectric loss even if the part being tested is intended for use with a lower quality PCB material.

<sup>3.</sup> Or  $25\Omega$  for lines with double termination.

Figure 3.9: Effect of input offset voltage on timing accuracy

This is problematic because high-speed interfaces actively limit the slew rate to minimize crosstalk, reflections and self-induced di/dt noise.

One solution to this problem is to make the sampler devices small to maximize the input bandwidth and then calibrate the samplers to reduce the offset voltage. In effect, this is trading an AC problem for a DC problem. But DC problems are typically easier to solve and therefore the trade-off results in a net benefit. The problem then becomes one of implementing offset compensation in a large number of samplers in a manner that is stable and relatively inexpensive so that the capacitive reduction due to decreased input gate area is not offset by the need for increased wire routing on the input signal.

## 3.6 Summary

Sampling resolution is the primary limitation to achieving high timing accuracy in an oversampled system. Time-interleaving samplers increase the effective sampling rate but also increase input capacitance which can cause timing errors. So while parallelism is useful, it is still desirable to clock the samplers at a very high rate. In CMOS, clocks are limited to about eight FO-4 delays.

Static phase offset and jitter reduce the timing accuracy of the system. Due to the static nature of phase offsets, they can be minimized with calibration. Deterministic jitter caused by power supply noise is a significant source of error in the clock generator. But an oversampled system captures edge transitions, and therefore, it is possible to measure the sampling system jitter and cancel it on a cycle by cycle basis. Sampler offsets are a source of slew-rate dependant timing errors and, as with static phase errors, can be reduced with a

calibration sequence performed prior to operation. The next chapter details a test chip built to investigate the trade-offs and issues encountered when implementing these techniques along. The chapter also includes test measurements to determine the achievable timing accuracy. 3.6 Summary

# **Implementation and Timing Peformance**

"I have not failed 10,000 times. I have successfully found 10,000 ways that will not work"

#### - Thomas Edison

The previous chapter examined implementation independent timing issues in an oversampled system. This chapter describes oversampled input receiver implementation details and measured lab results. The first section of this chapter provides an overview of the sampling system included on the test chip. The timing accuracy is primarily limited by the clock generators which are described in Section 4.2. This includes interpolation circuits for creating finely spaced clocks and architectural trade-offs for building multiphase clock generators with tunable output phases. The section concludes with test results for static phase and jitter compensation techniques for two clock generators. Having explored methods to build clock generators, Section 4.3 then examines clocked input samplers that can capture high-speed signals while having a minimal impact on timing accuracy.

## 4.1 Test Chip

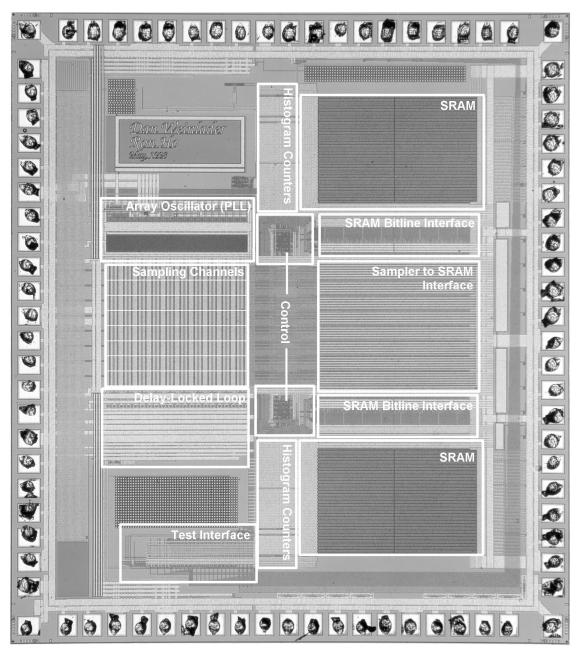

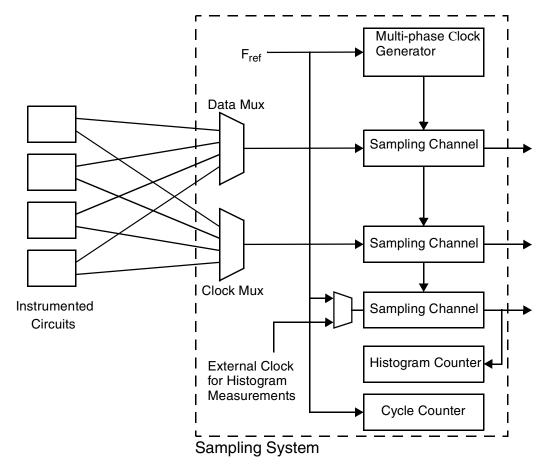

To better understand the trade-offs described in the previous chapter, and to test the compensation methods, a sampling receiver test chip was designed and measured. A block diagram of the test chip is shown in Figure 4.1. The part was fabricated in a standard 0.25µm, five metal layer process. It contains eight sampling channels that feed either an SRAM memory or an on-chip histogram counter. The sampling rate per channel is 36Gsamples/s with a 900MHz reference clock and 40 sampling phases. The eight sampling channels generate 288Gb/s of digital data but to reduce the required bandwidth of the acquisition memory, the data rate is reduced by oversampling only half the cycle. The memory is capable of storing the resulting 144Gb/s data stream with no further loss of information. The chip contains two circuits that can be used to generate the finely spaced (27ps) clocks. One uses a delay line with interpolation and the other uses an array of

Figure 4.1: Test chip block diagram

oscillators. Since the clock generators are the most critical circuits, they are discussed next.

## 4.2 Clock Generation

The clock generators drive the input sampling receivers and set the timing of the entire system. To compare design trade-offs and performance, both a phase-locked loop and delay-locked loop were included on the test chip. The performance of the delay elements in the clock generators significantly impacts the jitter performance, so this section starts with a description of a low-jitter differential delay element. The delay element is then transformed into a tunable interpolator to permit fine phase spacing. The section continues with a discussion of the issues involving the incorporation of tunable interpolators into a delay line and VCO to achieve a large adjustment range without compromising performance. The control loops and clock buffers are then described along with techniques to minimize the static phase offsets and jitter caused by these elements.

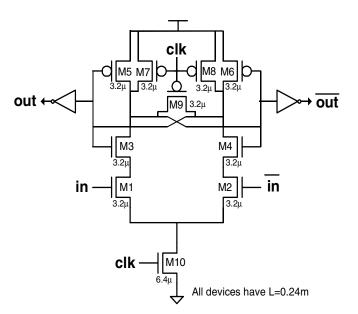

#### 4.2.1 Basic Elements

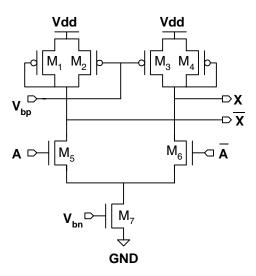

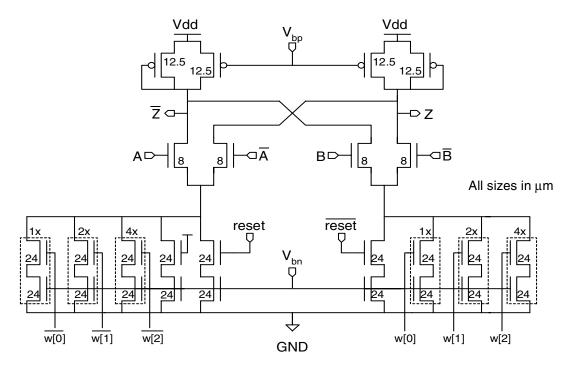

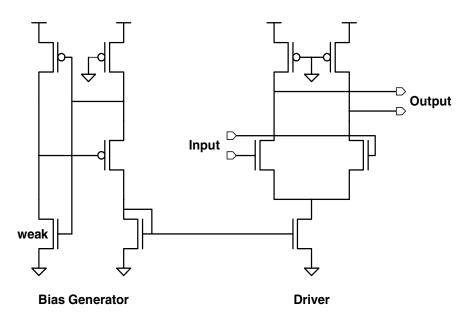

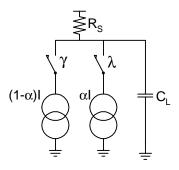

The clock generators are implemented with Maneatis style self-biased control loops and replica biased, variable delay, differential buffers with symmetric loads [25]. A buffer is shown in Figure 4.2. The two PMOS devices that form the load structures are termed symmetric loads in [23]. If the output swing is equal to the bias voltage  $V_{bp}$ , then the resistance of the loads is symmetric about the crossing of the differential outputs. This

Figure 4.2: Differential delay element

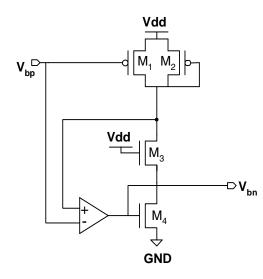

reduces the jitter caused by common-mode supply noise.  $V_{bp}$  is driven by the control loop, described in section 5.2.4, to set the delay of the buffer.  $V_{bn}$  is dynamically set by the replica biasing circuit in Figure 4.3 to set the output signal swing equal to  $V_{bp}$  which maintains the symmetric nature of the loads. The differential topology, symmetric loads, and replica biasing yields a delay element with a low sensitivity to supply noise. A standard inverter has a delay sensitivity of roughly 1, while this element has a delay sensitivity of about 0.05, which is an improvement by a factor of twenty.<sup>1</sup>

Figure 4.3: Replica bias generator for delay elements

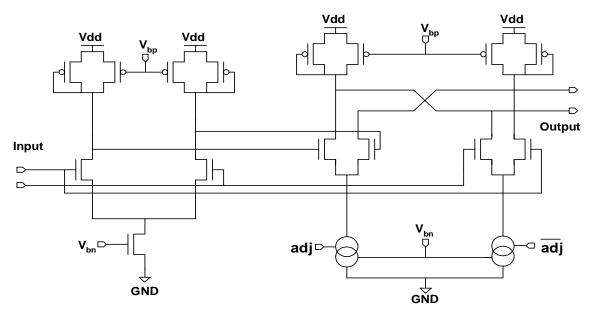

Figure 4.4: Differential interpolator

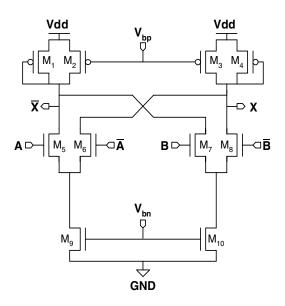

An interpolator can be built with two differential buffers by shorting their outputs together, as shown in Figure 4.4 [23]. In this figure, the PMOS loads from the two buffers have been merged and the A and B inputs are the clocks being interpolated. The output phase is set by the relative strengths of the two sides. While ideally all devices in the buffers should be scaled to change the output phase, only the size of the current source devices, M9 and M10, really matter. To maintain constant signal swings, the sum of the currents in the two current sources must remain constant.

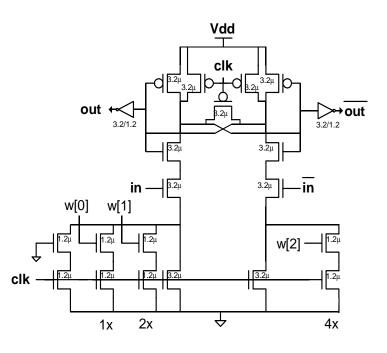

In previously published multi-phase clock generators, current sources M9 and M10 were fixed to a value that optimized the simulated phase spacing [37]. On the test chip, the current sources are implemented as 3-bit current DACs, as shown in Figure 4.5, to permit run-time adjustment of the clock phases. This adjustment allows for correction of small static errors in the clock phases. The DAC is binary rather than thermometer encoded because monotonicity is not required.<sup>1</sup> Standard matching techniques are used to layout

<sup>1.</sup> Recall delay sensitivity, as defined in Chapter 3, is the percent change in delay divided by the percent change in supply voltage and is unitless.

<sup>1.</sup> Previous application of the adjustable interpolators use a thermometer coded DAC to permit dynamic changes to the current weights [31]. However, for this application, the adjustment codes are only changed during an initial calibration sequence so less complex binary weighting is instead used. The DAC currents do not even have to be monotonic as the calibration algorithm can check all possible adjustment codes and pick the best one.

Figure 4.5: An adjustable interpolator with a 3-bit adjustment range

the tuning devices including dummy devices to minimize proximity effects, matched orientation, and larger devices composed of multiple copies of smaller devices. Matching data on the target process indicates that even with small devices, transistor mismatch does not significantly limit the adjustment resolution.

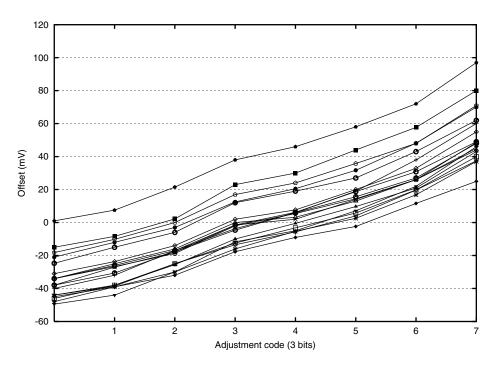

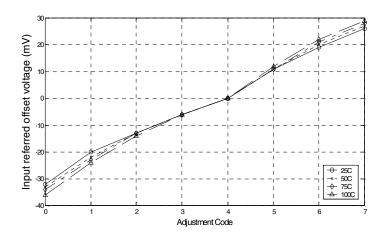

Incorporating phase adjustment into both the DLL and PLL while maintaining a large adjustment range is difficult. This is due to the phase adjustment range of an interpolator being limited by the phase spacing of the input signals. If the inputs have a small phase difference, then the output phase adjustment range will be corresponding small. The adjustment range is also limited by the nominal position of the output phase. Matching data and results from previously implemented clock generators [6][23][37] indicates static phase offsets of  $\pm 0.2$  of a buffer delay are to be expected, so the design goal was an adjustment range of  $\pm 0.25$  of a buffer delay. The next sub-sections describe how the interpolators are integrated into the clock generators to maintain sufficient adjustment range.

## 4.2.2 Delay-Line Based Clock Generator

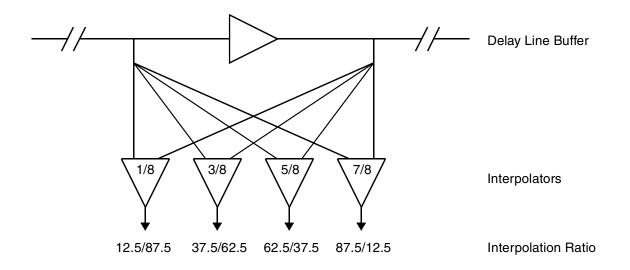

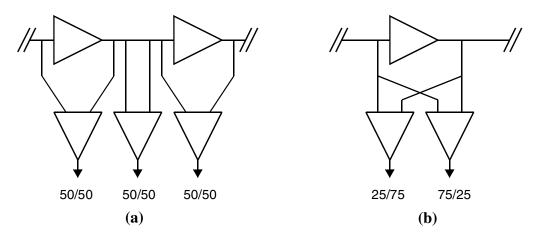

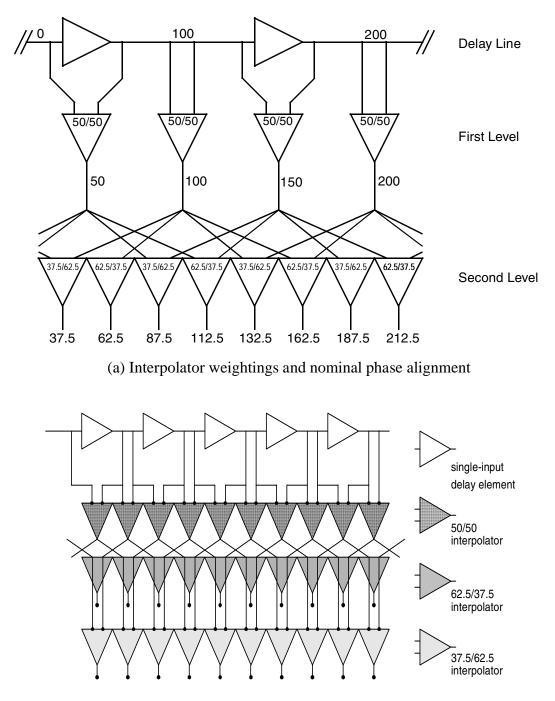

The core of the delay line is five differential delay elements. Interpolators split the five clock phases into twenty differential clocks. A single level of interpolation, as shown in Figure 4.6, minimizes jitter because it minimizes the delay through the clock paths as compared to techniques using multiple levels of interpolation. The interpolation ratios are chosen to maximize the adjustment range of all the interpolators. Nevertheless, this topology is unsatisfactory because the interpolators on the ends have a limited adjustment range of 1/8 a buffer delay one direction since their nominal position is within 12.5% of one of the input phases. To maintain a reasonable adjustment range, not only do the inputs to the interpolator need to have sufficient phase spacing, but the nominal weighting of the interpolators must not be excessively skewed from 1/2.

Figure 4.6: Initial interpolation strategy for DLL